PIC32CM5164JH01032

PIC32CM5164JH01032 is 32-bit Arm Cortex-M0+ manufactured by Microchip Technology.

- Part of the PIC32CM2532JH01032 comparator family.

- Part of the PIC32CM2532JH01032 comparator family.

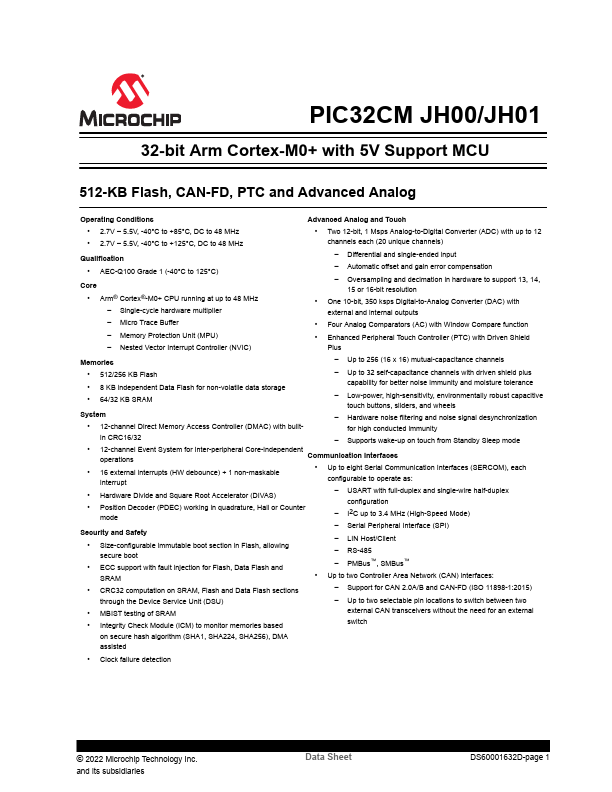

PIC32CM JH00/JH01

32-bit Arm Cortex-M0+ with 5V Support MCU

512-KB Flash, CAN-FD, PTC and Advanced Analog

Operating Conditions

Advanced Analog and Touch

- 2.7V

- 5.5V, -40°C to +85°C, DC to 48 MHz

- 2.7V

- 5.5V, -40°C to +125°C, DC to 48 MHz

Qualification

- AEC-Q100 Grade 1 (-40°C to 125°C)

Core

- Arm® Cortex®-M0+ CPU running at up to 48 MHz

- Single-cycle hardware multiplier

- Micro Trace Buffer

- Memory Protection Unit (MPU)

- Nested Vector Interrupt Controller (NVIC)

- Two 12-bit, 1 Msps Analog-to-Digital Converter (ADC) with up to 12 channels each (20 unique channels)

- Differential and single-ended input

- Automatic offset and gain error pensation

- Oversampling and decimation in hardware to support 13, 14, 15 or 16-bit resolution

- One 10-bit, 350 ksps Digital-to-Analog Converter (DAC) with external and internal outputs

- Four Analog parators (AC) with Window pare function

- Enhanced Peripheral Touch Controller (PTC) with Driven Shield

Plus

Memories

- Up to 256 (16 x 16) mutual-capacitance channels

- 512/256 KB Flash

- Up to 32 self-capacitance channels with driven shield plus

- 8 KB independent Data Flash for non-volatile data storage capability for better noise immunity and moisture tolerance

- 64/32 KB SRAM

- Low-power, high-sensitivity, environmentally robust capacitive touch buttons, sliders, and wheels

System

- Hardware noise filtering and noise signal desynchronization

- 12-channel Direct Memory Access Controller (DMAC) with built- for high conducted immunity in CRC16/32

- Supports wake-up on touch from Standby Sleep mode

- 12-channel Event System for Inter-peripheral Core-independent operations munication Interfaces

- 16 external interrupts (HW debounce) + 1 non-maskable interrupt

- Up to eight Serial munication Interfaces (SER), each configurable to operate as:

- Hardware Divide and Square Root Accelerator...