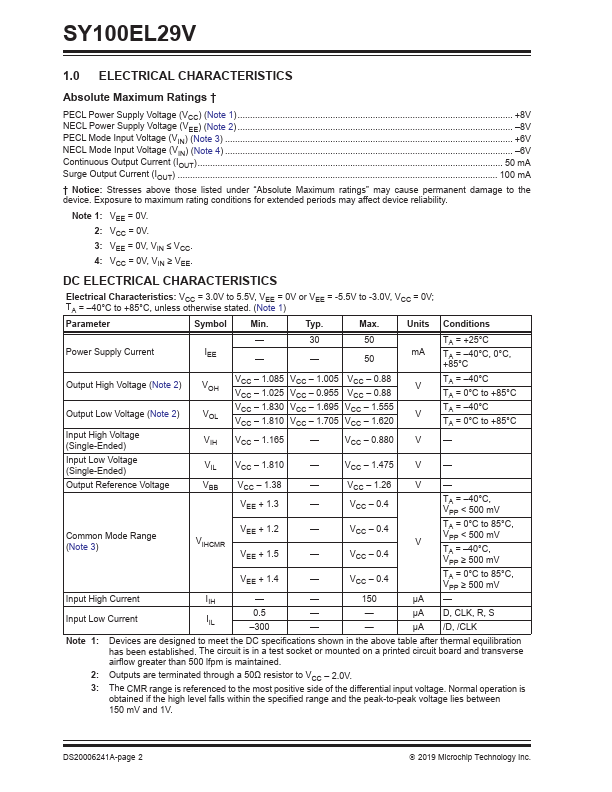

SY100EL29V Overview

The SY100EL29V is a dual differential register with differential data (inputs and outputs) and clock. The registers are triggered by a positive transition of the positive clock (CLK) input. A HIGH on the Reset (Rx) asynchronously resets the appropriate register so that the Q outputs go LOW.

SY100EL29V Key Features

- 3.3V and 5V Power Supply Option

- Differential D, CLK and Q

- Extended VEE Range of -3.0V to -5.5V

- VBB Output for Single-Ended Use

- 1100 MHz Min. Toggle Frequency

- Asynchronous Reset and Set

- Available in 20-Pin SOIC Package