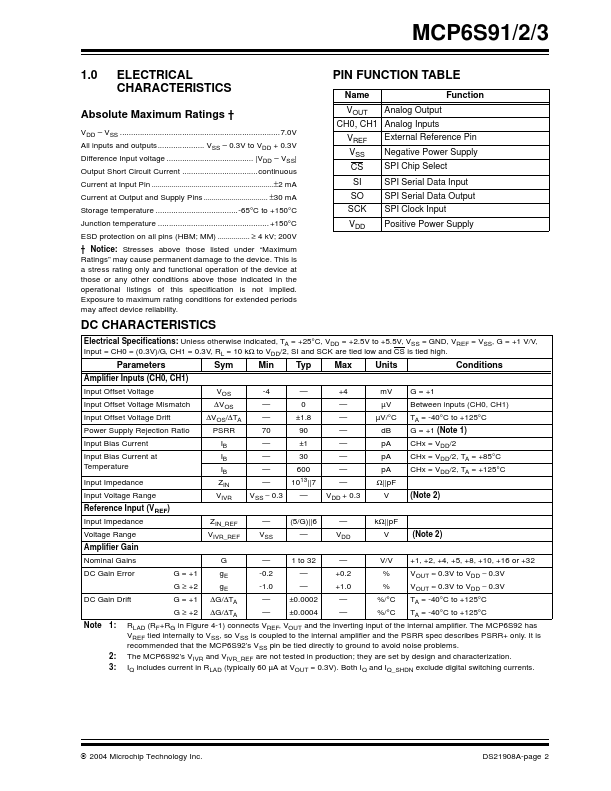

MCP6S92 Description

The Microchip Technology Inc. MCP6S91/2/3 are analog Programmable Gain Amplifiers (PGAs). They can be configured for gains from +1 V/V to +32 V/V and the input multiplexer can select one of up to two channels through a SPI port.

MCP6S92 Key Features

- Multiplexed Inputs: 1 or 2 channels

- 8 Gain Selections

- +1, +2, +4, +5, +8, +10, +16 or +32 V/V

- Serial Peripheral Interface (SPI™)

- Rail-to-Rail Input and Output

- Low Gain Error: ±1% (max.)

- Offset Mismatch Between Channels: 0 µV

- High Bandwidth: 1 to 18 MHz (typ.)

- Low Noise: 10 nV/√Hz @ 10 kHz (typ.)

- Low Supply Current: 1.0 mA (typ.)