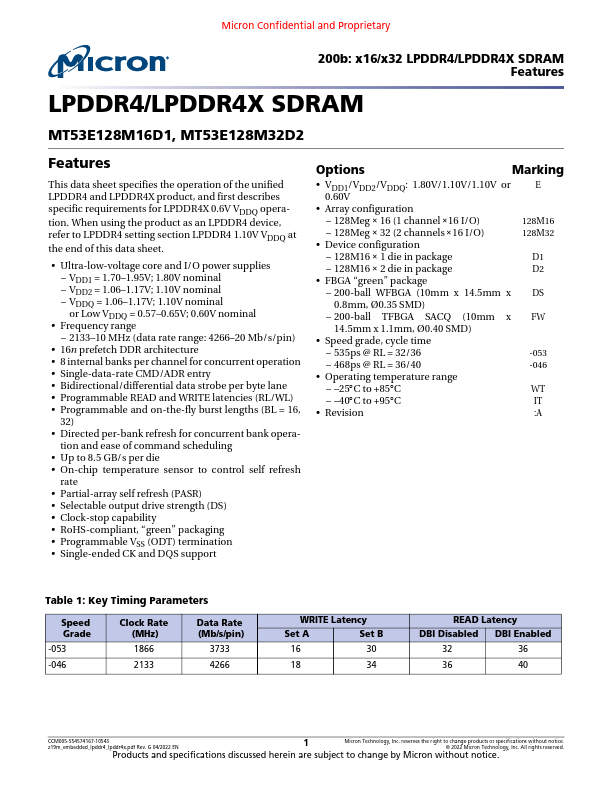

MT53E128M16D1 Overview

Key Specifications

Package: TFBGA

Operating Voltage: 1.1 V

Max Voltage (typical range): 1.17 V

Min Voltage (typical range): 1.06 V

Key Features

- Frequency range – 2133–10 MHz (data rate range: 4266–20 Mb/s/pin)

- 16n prefetch DDR architecture

- 8 internal banks per channel for concurrent operation

- Single-data-rate CMD/ADR entry

- Bidirectional/differential data strobe per byte lane

- Programmable READ and WRITE latencies (RL/WL)

- Programmable and on-the-fly burst lengths (BL = 16

- Directed per-bank refresh for concurrent bank opera- tion and ease of command scheduling

- Up to 8.5 GB/s per die

- On-chip temperature sensor to control self refresh rate