MT47H512M8 Description

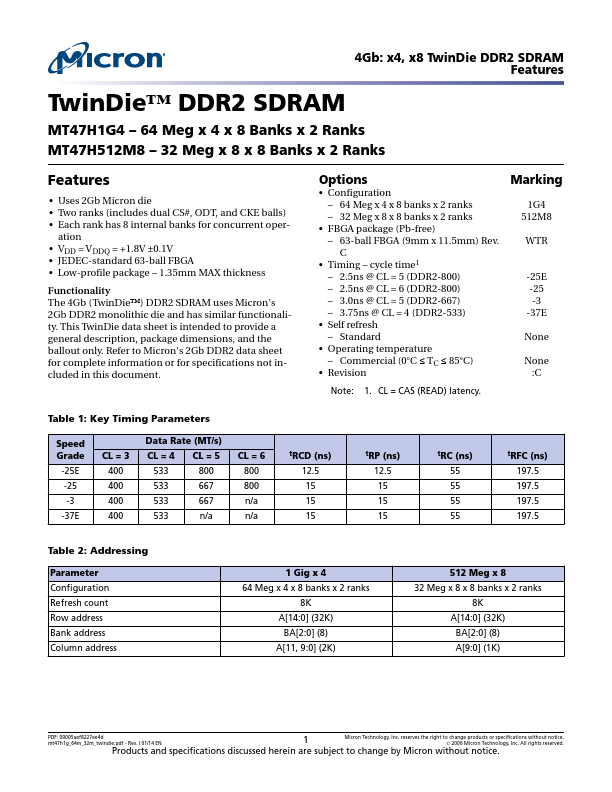

, package dimensions, and the ballout only. Refer to Micron's 2Gb DDR2 data sheet for plete information or for specifications not included in this document. Marking 1G4 512M8 WTR -25E -25 -3 -37E None None :C Table.

MT47H512M8 Key Features

- 64 Meg x 4 x 8 Banks x 2 Ranks MT47H512M8

- 32 Meg x 8 x 8 Banks x 2 Ranks Features

- Uses 2Gb Micron die

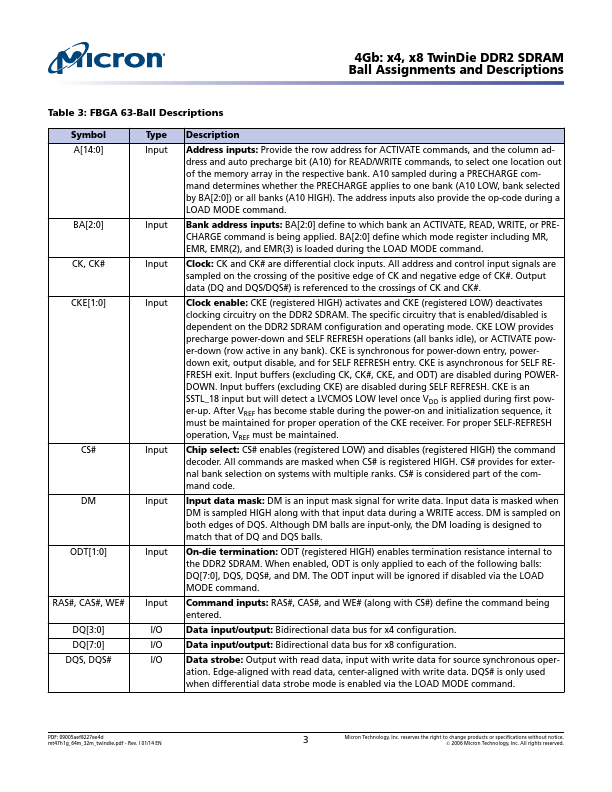

- Two ranks (includes dual CS#, ODT, and CKE balls)

- Each rank has 8 internal banks for concurrent operation

- VDD = V DDQ = +1.8V ±0.1V

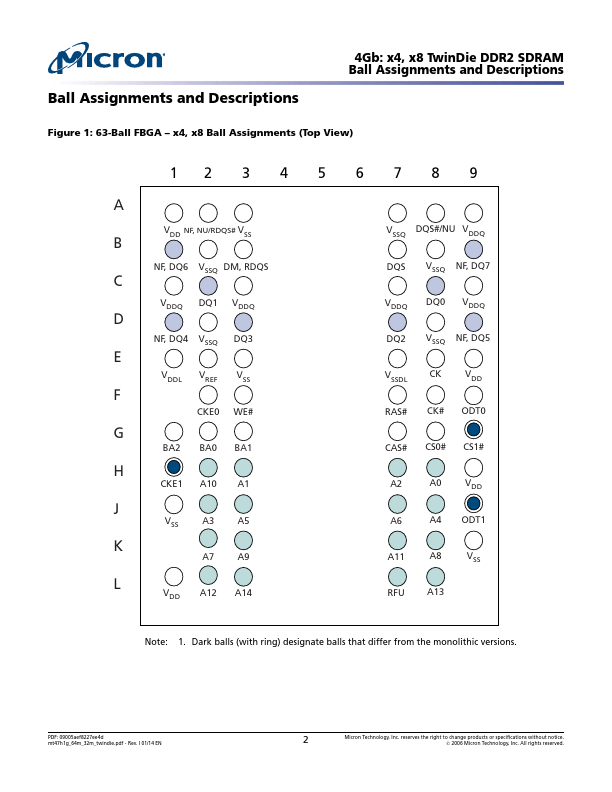

- JEDEC-standard 63-ball FBGA

- Low-profile package

- 1.35mm MAX thickness Functionality The 4Gb (TwinDie™) DDR2 SDRAM uses Micron’s 2Gb DDR2 monolithic die and has similar f

- Configuration