MT4C4M4E9 Description

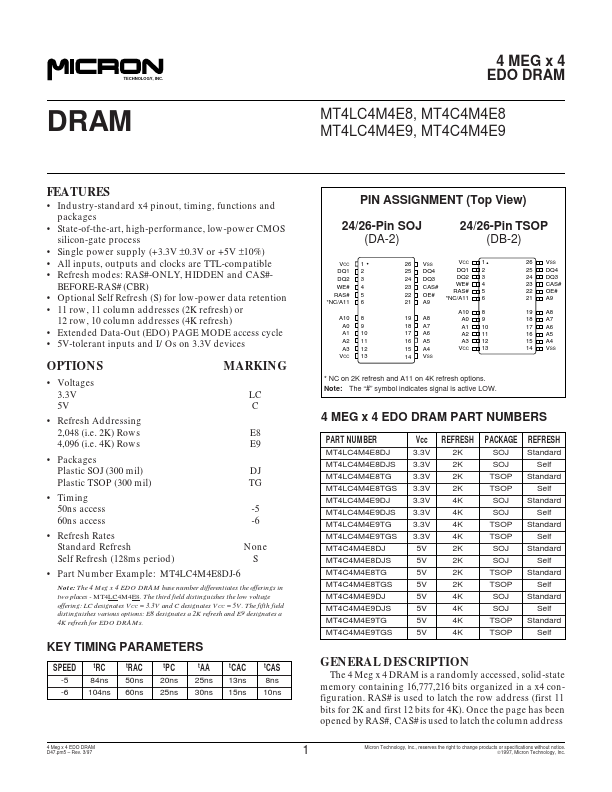

The 4 Meg x 4 DRAM is a randomly accessed, solid-state memory containing 16,777,216 bits organized in a x4 configuration. RAS# is used to latch the row address (first 11 bits for 2K and first 12 bits for 4K). 3/97 1 Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT4C4M4E9 Key Features

- Industry-standard x4 pinout, timing, functions and packages

- State-of-the-art, high-performance, low-power CMOS silicon-gate process

- Single power supply (+3.3V ±0.3V or +5V ±10%)

- All inputs, outputs and clocks are TTL-patible

- Refresh modes: RAS#-ONLY, HIDDEN and CAS#BEFORE-RAS# (CBR)

- Optional Self Refresh (S) for low-power data retention

- 11 row, 11 column addresses (2K refresh) or 12 row, 10 column addresses (4K refresh)

- Extended Data-Out (EDO) PAGE MODE access cycle

- 5V-tolerant inputs and I/Os on 3.3V devices

- Voltages 3.3V 5V