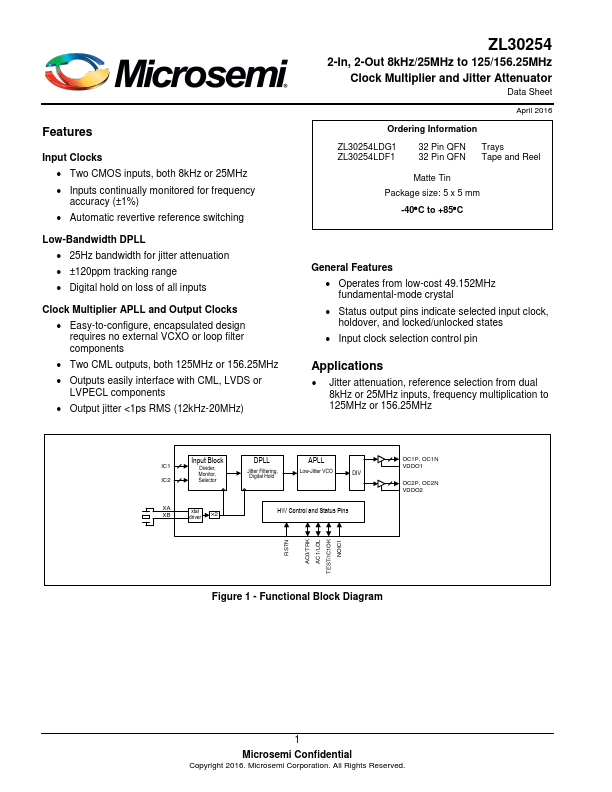

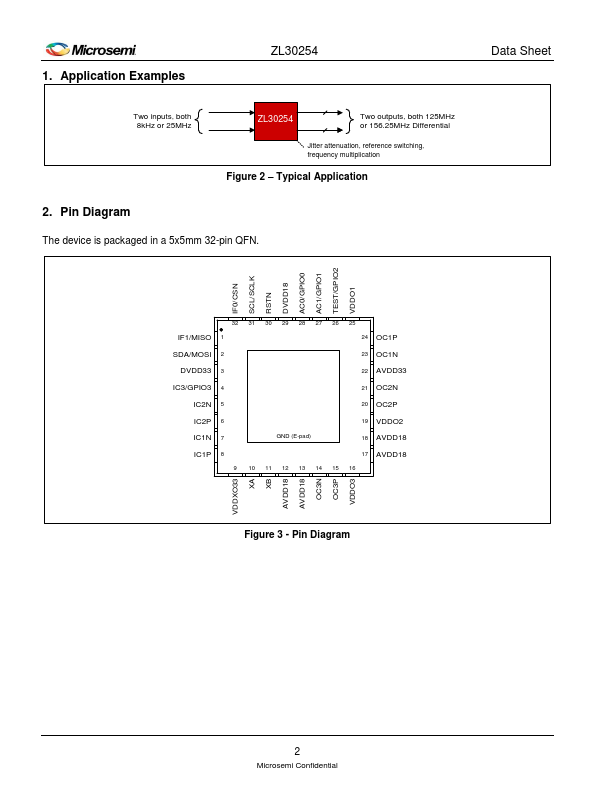

ZL30254 Overview

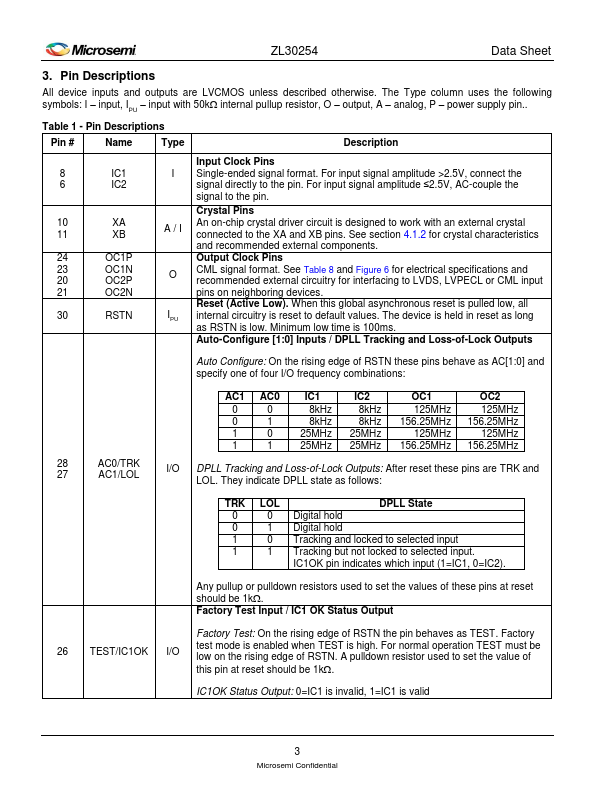

Input Clock Pins 8 IC1 I Single-ended signal format. For input signal amplitude >2.5V, connect the 6 IC2 signal directly to the pin. For input signal amplitude ≤2.5V, AC-couple the signal to the pin.

ZL30254 Key Features

- Two CMOS inputs, both 8kHz or 25MHz

- Inputs continually monitored for frequency accuracy (±1%)

- Automatic revertive reference switching

- 25Hz bandwidth for jitter attenuation

- ±120ppm tracking range

- Digital hold on loss of all inputs

- Easy-to-configure, encapsulated design requires no external VCXO or loop filter ponents

- Two CML outputs, both 125MHz or 156.25MHz

- Outputs easily interface with CML, LVDS or LVPECL ponents

- Output jitter <1ps RMS (12kHz-20MHz)