Datasheet Summary

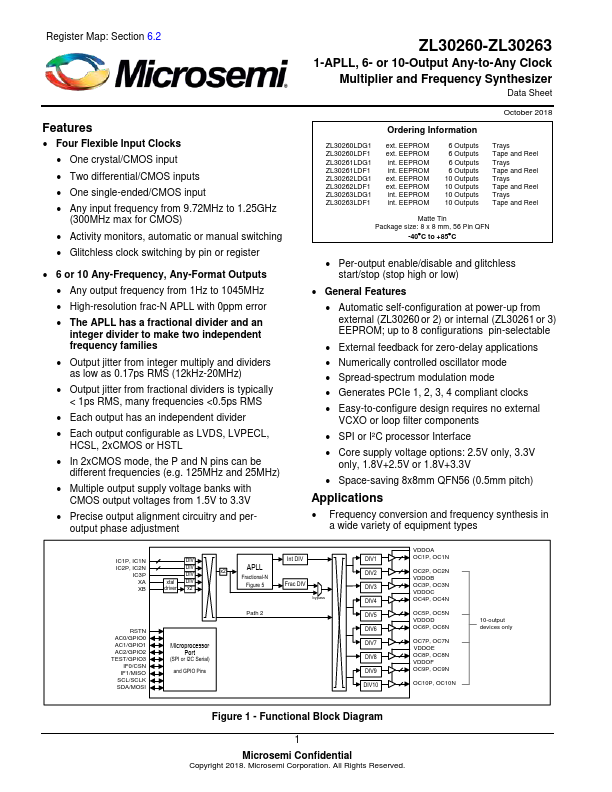

Register Map: Section 6.2

Features

- Four Flexible Input Clocks

- One crystal/CMOS input

- Two differential/CMOS inputs

- One single-ended/CMOS input

- Any input frequency from 9.72MHz to 1.25GHz (300MHz max for CMOS)

- Activity monitors, automatic or manual switching

- Glitchless clock switching by pin or register

- 6 or 10 Any-Frequency, Any-Format Outputs

- Any output frequency from 1Hz to 1045MHz

- High-resolution frac-N APLL with 0ppm error

- The APLL has a fractional divider and an integer divider to make two independent frequency families

- Output jitter from integer multiply and dividers as low as 0.17ps RMS (12kHz-20MHz)

- Output jitter from fractional dividers is typically < 1ps...