LS842 Description

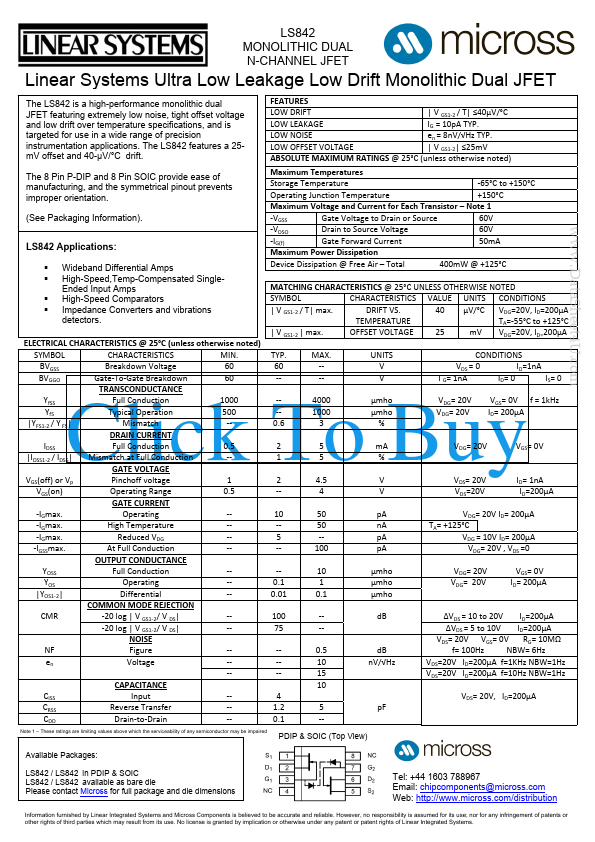

LS842 MONOLITHIC DUAL N-CHANNEL JFET Linear Systems Ultra Low Leakage Low Drift Monolithic Dual JFET The LS842 is a high-performance monolithic dual JFET featuring extremely low noise, tight offset voltage and low drift over temperature specifications, and is targeted for use in a wide range of precision instrumentation applications.

LS842 Key Features

- Note 1 ‐VGSS Gate Voltage to Drain or Source 60V ‐VDSO Drain to Source Voltage 60V ‐IG(f) Gate Forward Current

LS842 Applications

- Note 1 ‐VGSS Gate Voltage to Drain or Source 60V ‐VDSO Drain to Source Voltage 60V ‐IG(f) Gate Forward Current 50mA Maximum Power Dissipation Device