M5M5V5636GP16 Overview

Description

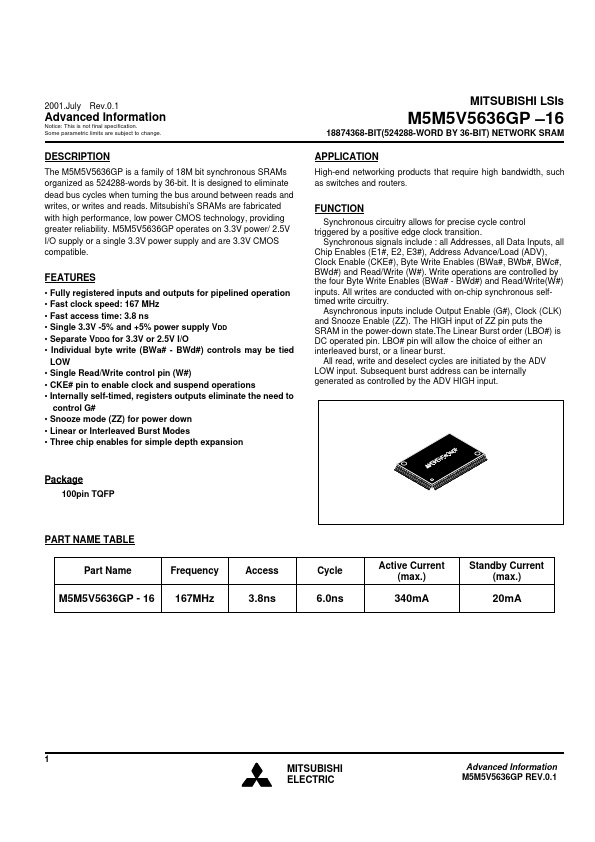

The M5M5V5636GP is a family of 18M bit synchronous SRAMs organized as 524288-words by 36-bit. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads.

Key Features

- Fully registered inputs and outputs for pipelined operation

- Fast clock speed: 167 MHz

- Fast access time: 3.8 ns

- Single 3.3V -5% and +5% power supply VDD

- Separate VDDQ for 3.3V or 2.5V I/O

- Individual byte write (BWa#

- BWd#) controls may be tied LOW