M5M82C37AP-4 Overview

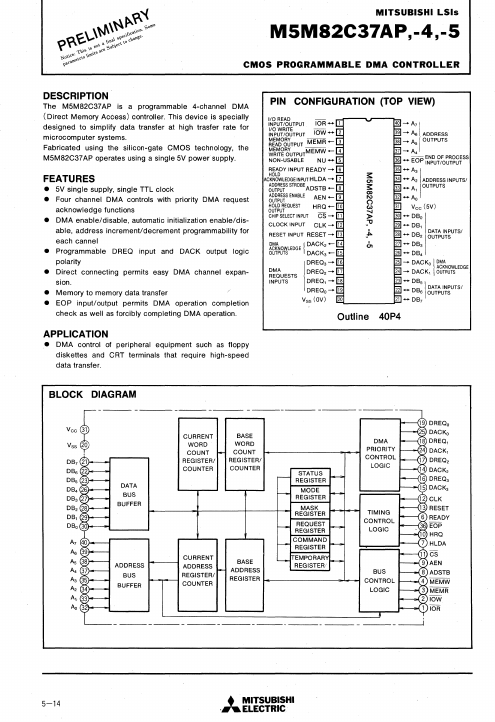

The M5M82C37AP is a programmable 4-channel DMA (Direct Memory Access) controller. This device is specially designed to simplify data transfer at high trasfer rate for microputer systems. Fabricated using the silicon-gate CMOS technology, the M5M82C37AP operates using a single 5V power supply.

M5M82C37AP-4 Key Features

- 5V single supply, single TTL clock

- Four channel DMA controls with priority DMA request

- DMA enable/disable, automatic initialization enable/dis

- Programmable DREQ input and DACK output logic polarity

- Direct connecting permits easy DMA channel expansion

- Memory to memory data transfer

- EOP input/output permits DMA operation pletion check as well as forcibly pleting DMA operation

- DMA control of peripheral equipment such as floppy diskettes and CRT terminals that require hig