M66282FP

Overview

The M66282FP is high speed line memory that uses high performance silicon gate CMOS process technology and adopts the FIFO (First In First Out) structure consisting of 8192 words x 8 bits. The M66282FP, performing reading and writing operations at different cycles independently and asynchronously, is optimal for buffer memory to be used between equipment of different data processing speeds.

- Memory configuration 8192 words x 8 bits (dynamic memory) High speed cycle 25 ns (Min.) High speed access 18 ns (Max.) Output hold 3 ns (Min.) Reading and writing operations can be completely carried out independently and asynchronously.

- Variable length delay bit

- Input/output TTL direct connection allowable

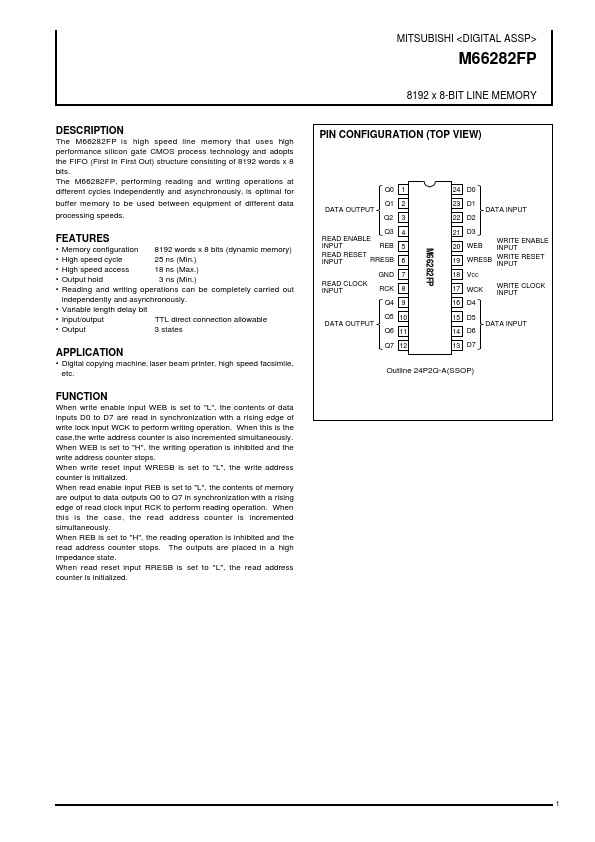

- Output 3 states M66282FP