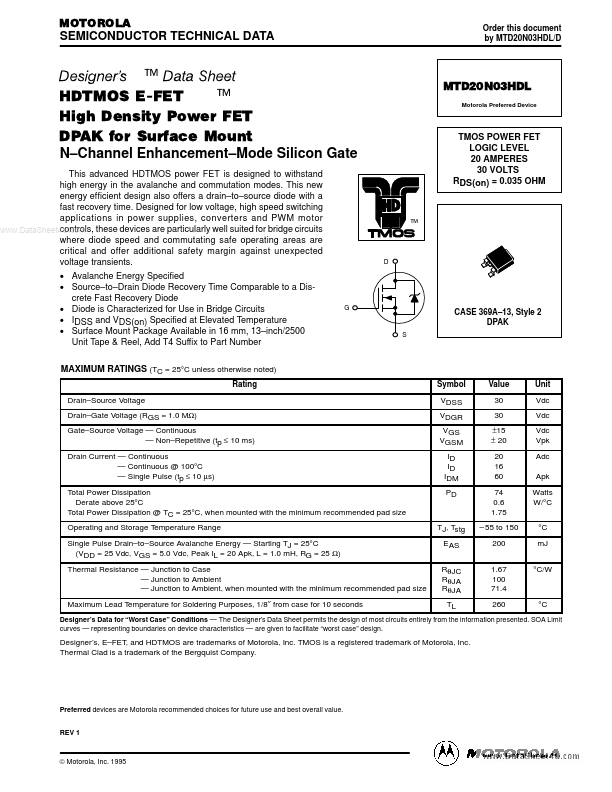

| Part | 20N03HL |

|---|---|

| Description | MTD20N03HL |

| Manufacturer | Motorola Semiconductor |

| Size | 206.39 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 20N03L | Infineon | IPD20N03L |

| 20N03 | Inchange Semiconductor | N-Channel MOSFET |

| 20N06 | Inchange Semiconductor | N-Channel MOSFET |

| 20N06 | onsemi | N-Channel MOSFET |

| PSR-20N08A-JQ | MALLORY | Miniature Speaker |