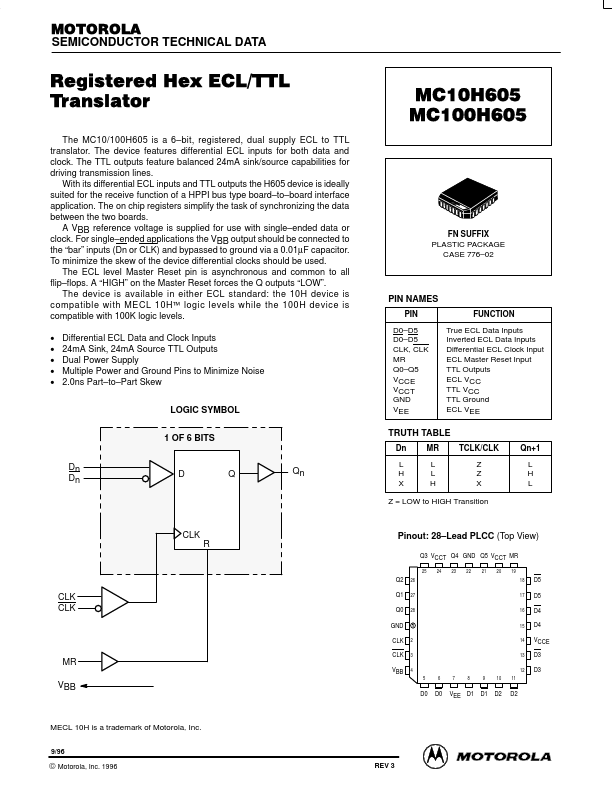

MC100H605

features differential ECL inputs for both data and clock. The TTL outputs feature balanced 24m A sink/source capabilities for driving transmission lines.

With its differential ECL inputs and TTL outputs the H605 device is ideally suited for the receive function of a HPPI bus type board- to- board interface application. The on chip registers simplify the task of synchronizing the data between the two boards.

A VBB reference voltage is supplied for use with single- ended data or clock. For single- ended applications the VBB output should be connected to the “bar” inputs (Dn or CLK) and bypassed to ground via a 0.01µF capacitor. To minimize the skew of the device differential clocks should be used.

The ECL level Master Reset pin is asynchronous and mon to all flip- flops. A “HIGH” on the Master Reset forces the...