MC14469 Description

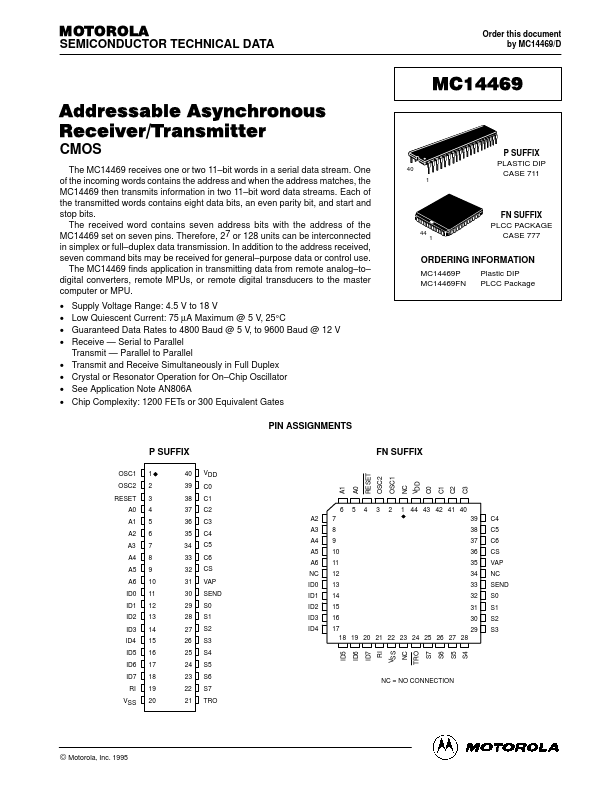

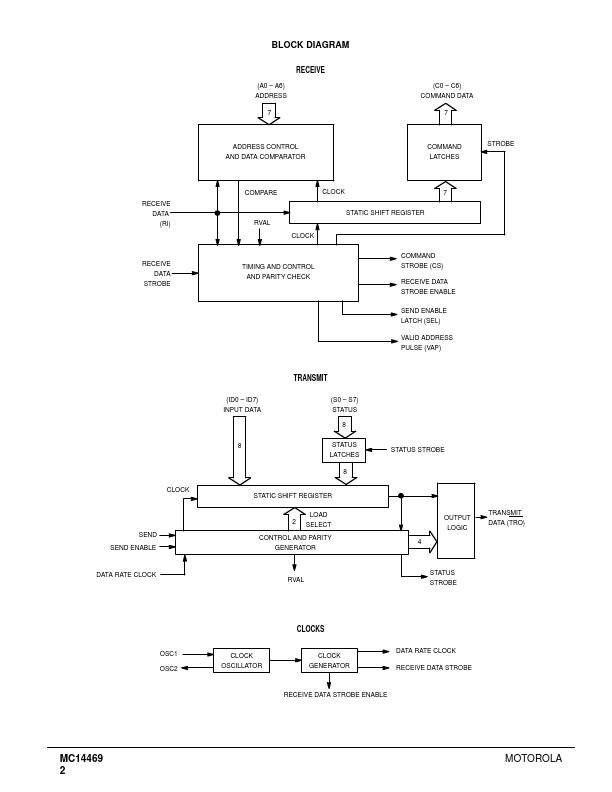

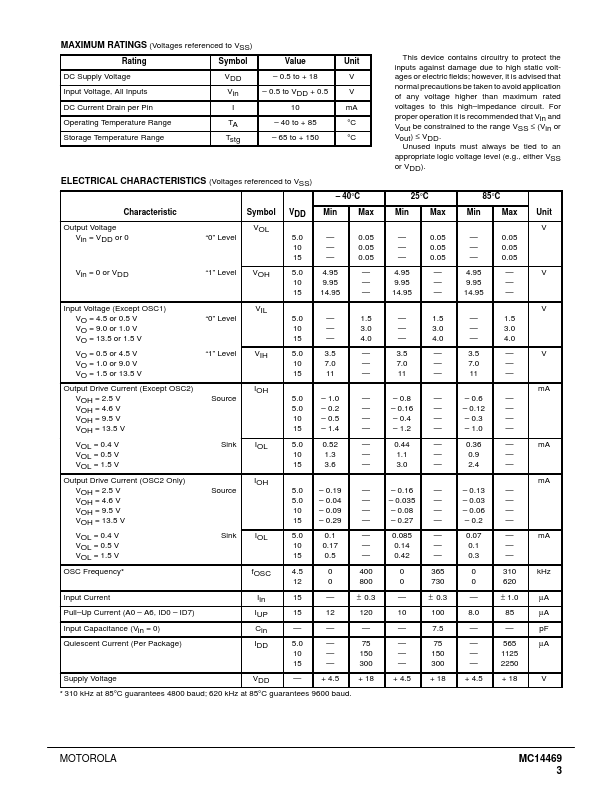

MOTOROLA SEMICONDUCTOR TECHNICAL DATA Order this document by MC14469/D MC14469 Addressable Asynchronous Receiver/Transmitter CMOS The MC14469 receives one or two 11 bit words in a serial data stream. One of the ining words contains the address and when the address matches, the MC14469 then transmits information in two 11 bit word data streams. Each of the transmitted words contains eight data bits, an even parity...