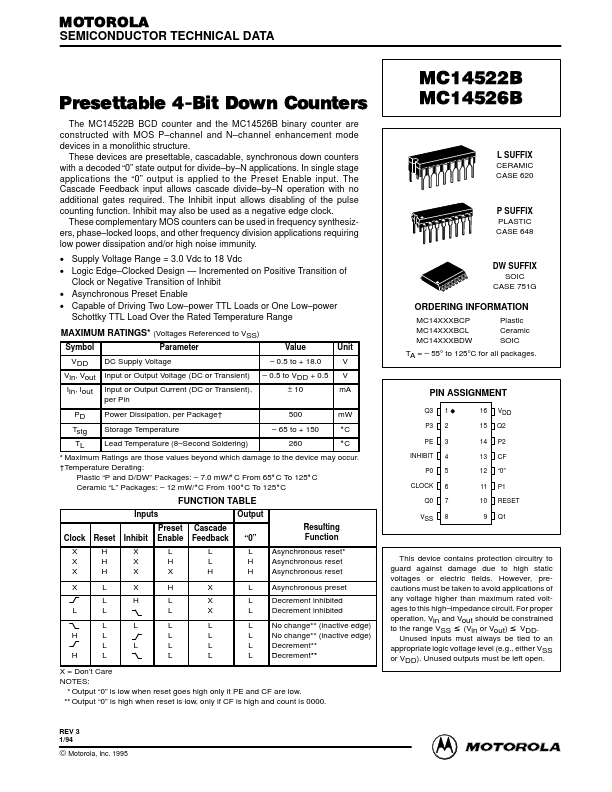

| Part | MC14522B |

|---|---|

| Description | Presettable 4-Bit Down Counters |

| Manufacturer | Motorola Semiconductor |

| Size | 272.84 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MC14520B | onsemi | Dual Up Counters |

| MC14528B | onsemi | Dual Monostable Multivibrator |

| MC14526B | onsemi | Presettable 4-Bit Down Counters |

| MC14521B | onsemi | 24-Stage Frequency Divider |