MCK12140D

MCK12140D is PHASE-FREQUENCY DETECTOR manufactured by Motorola Semiconductor.

Order this document By MCH12140/D

PhaseĆFrequency Detector

The MCH/K12140 is a phase frequency-detector intended for phase-locked loop applications which require a minimum amount of phase and frequency difference at lock. When used in conjunction with the MC12147, MC12148 or MC12149 VCO, a high bandwidth PLL can be realized. The device is functionally patible with the MC12040 phase-frequency detector, however the MOSAIC™ III process is used to push the maximum frequency to 800 MHz and significantly reduce the dead zone of the detector. When the Reference (R) and VCO (V) inputs are unequal in frequency and/or phase, the differential UP (U) and DOWN (D) outputs will provide pulse streams which when subtracted and integrated provide an error voltage for control of a VCO. The device is packaged in a small outline, surface mount 8-lead SOIC package. There are two versions of the device to provide I/O patibility to the two existing ECL standards. The MCH12140 is patible with MECL10H™ logic levels while the MCK12140 is patible to 100K ECL logic levels. This device can also be used in +5.0 V systems. Please refer to Motorola Application Note AN1406/D, “Designing with PECL (ECL at +5.0 V)” for more information.

MCH12140 MCK12140

PHASE- FREQUENCY DETECTOR

SEMICONDUCTOR TECHNICAL DATA

8 1

- -

- -

800 MHz Typical Bandwidth Small Outline 8-Lead SOIC Package 75 kΩ Internal Input Pulldown Resistors >1000 V ESD Protection

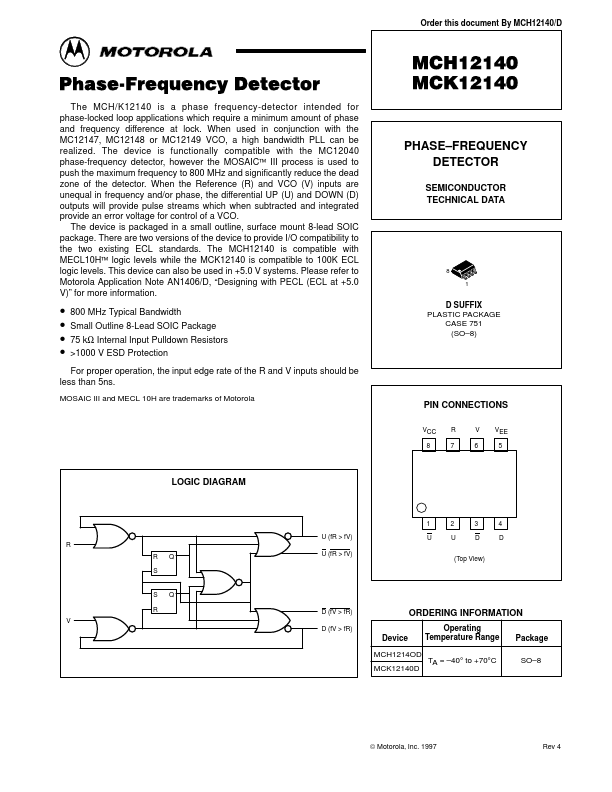

D SUFFIX PLASTIC PACKAGE CASE 751 (SO- 8)

For proper operation, the input edge rate of the R and V inputs should be less than 5ns.

MOSAIC III and MECL 10H are trademarks of Motorola

PIN CONNECTIONS

VCC 8 R 7 V 6 VEE 5

LOGIC DIAGRAM

1 U (f R > f V) R R S S R V D (f V > f R) Device MCH1214OD MCK12140D Q D (f V > f R) Q U (f R > f V) U

2 U

3 D

4 D

(Top View)

ORDERING INFORMATION

Operating Temperature Range TA =

- 40° to +70°C Package SO- 8

© Motorola, Inc. 1997

Rev 4

MCH12140 MCK12140

TRUTH TABLE-

Input R 0 0 1 0 1 0 1 1 V 0 1 1 1 1 1 1 0 U X X X X 1 1 1 1 D X...