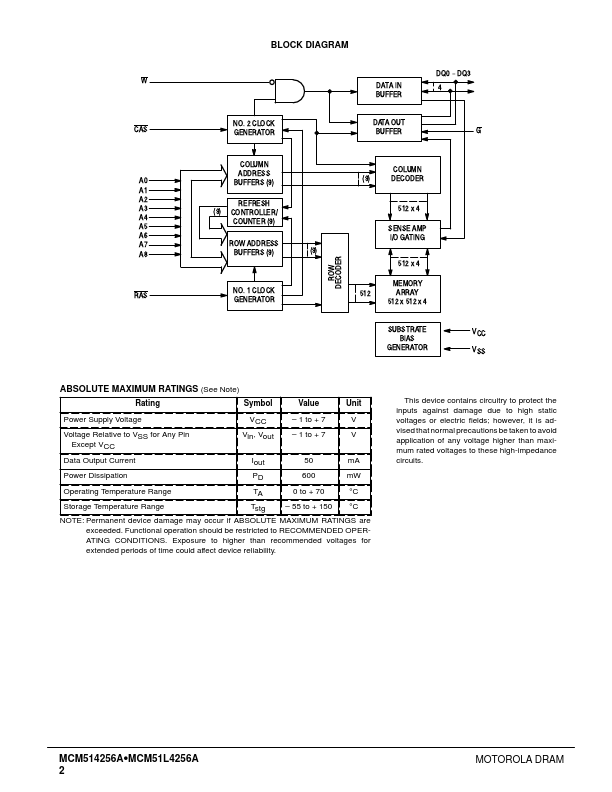

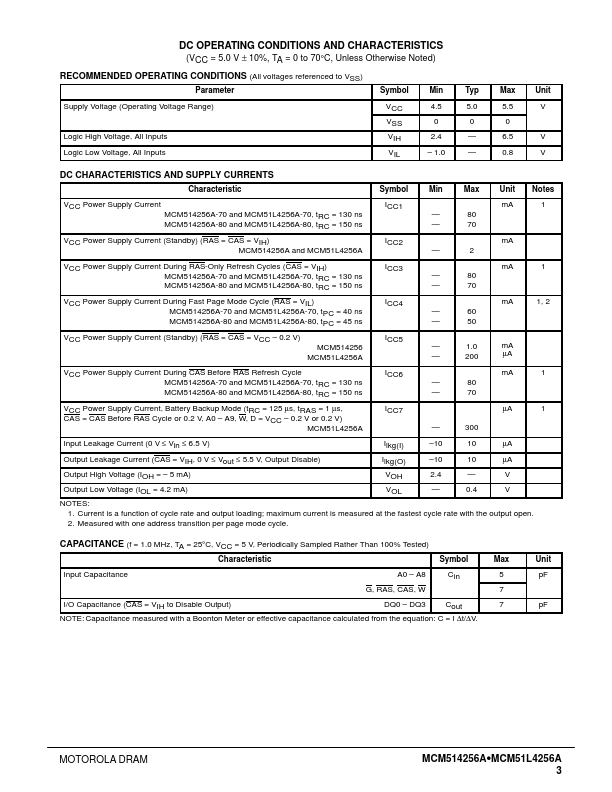

Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

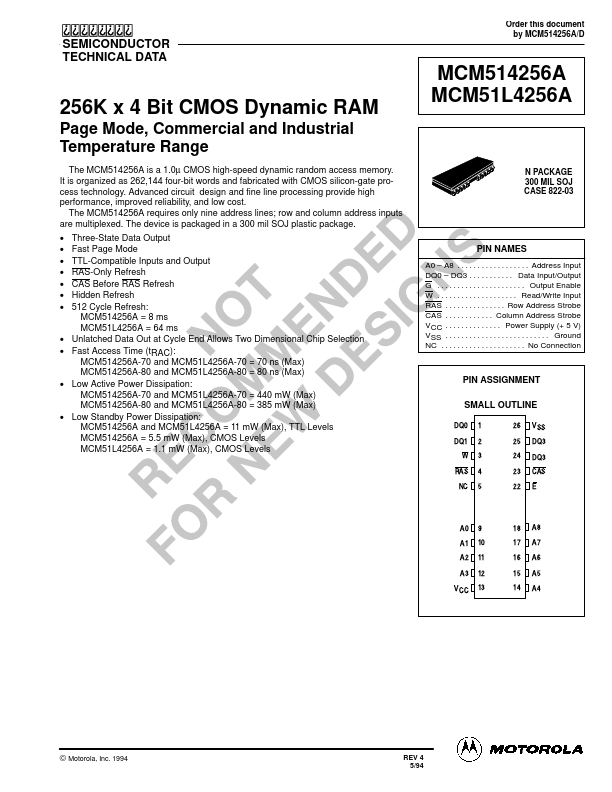

256K x 4 Bit CMOS Dynamic RAM

Page Mode, mercial and Industrial Temperature Range

The MCM514256A is a 1.0µ CMOS high-speed dynamic random access memory. It is organized as 262,144 four-bit words and fabricated with CMOS silicon-gate process technology. Advanced circuit design and fine line processing provide high performance, improved reliability, and low cost.

The MCM514256A requires only nine address lines; row and column address inputs are multiplexed. The device is packaged in a 300 mil SOJ plastic package.

- Three-State Data Output

- Fast Page Mode

- TTL-patible Inputs and Output

- RAS-Only Refresh

- CAS Before RAS Refresh

- Hidden Refresh

-...