D720133 Description

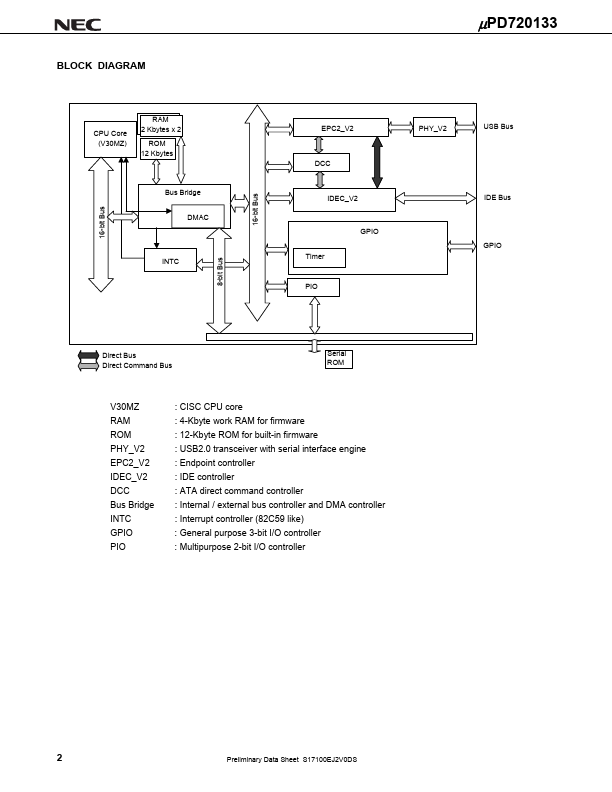

PRELIMINARY DATA SHEET MOS INTEGRATED CIRCUIT µPD720133 USB2.0 to IDE Bridge The µPD720133 is designed to function as a bridge between USB 2.0 and ATA/ATAPI. The µPD720133 plies with the Universal Serial Bus Specification Revision 2.0 full-/high-speed signaling and works up to 480 Mbps. The µPD720133 consists of a CISC processor, an ATA/ATAPI controller, an endpoint controller (EPC), a serial interface engine (SIE),...

D720133 Key Features

- pliant with Universal Serial Bus Specification Revision 2.0 (Data Rate 12/480 Mbps)

- USB2.0 high-speed bus powered device capability

- Certified by USB implementers forum and granted with USB 2.0 high-speed Logo (TID: 40001985)

- One USB2.0 high-speed transceiver / receiver with full-speed transceiver / receiver

- USB2.0 High-speed or Full-speed packet protocol sequencer (Serial Interface Engine)

- Automatic chirp assertion and full-/high-speed mode change

- USB Reset, Suspend and Resume signaling detection

- Supports power control functionality for IDE device as CD-ROM and HDD

- Supports set feature (TEST_MODE) functionality

- System Clock is generated by 30 MHz X’tal