UPD42S17405LLA-A50

Description

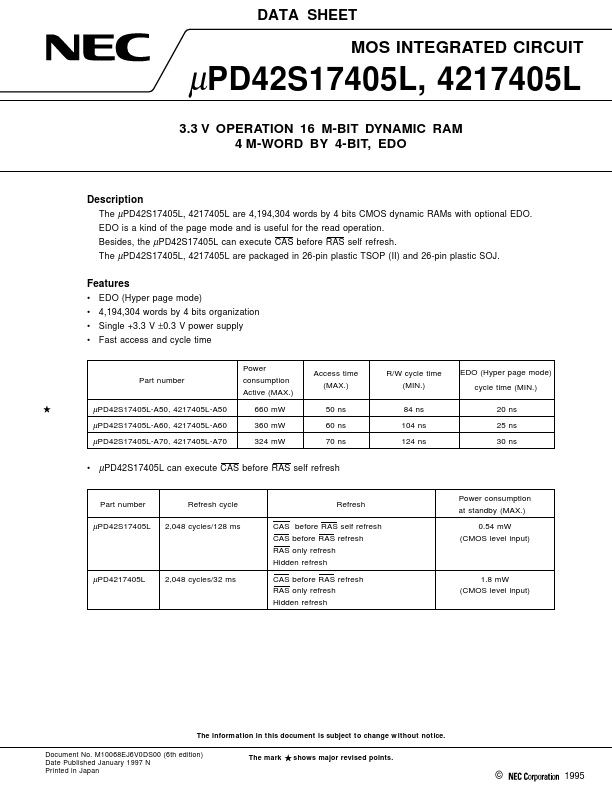

The µPD42S17405L, 4217405L are 4,194,304 words by 4 bits CMOS dynamic RAMs with optional EDO. EDO is a kind of the page mode and is useful for the read operation.

Key Features

- EDO (Hyper page mode)

- 4,194,304 words by 4 bits organization

- Single +3.3 V ±0.3 V power supply

- Fast access and cycle time Power consumption Active (MAX.) 660 mW 360 mW 324 mW Part number Access time (MAX.) 50 ns 60 ns 70 ns R/W cycle time (MIN.) 84 ns 104 ns 124 ns EDO (Hyper page mode) cycle time (MIN.) 20 ns 25 ns 30 ns µPD42S17405L-A50, 4217405L-A50 µPD42S17405L-A60, 4217405L-A60 µPD42S17405L-A70, 4217405L-A70

- µPD42S17405L can execute CAS before RAS self refresh Power consumption at standby (MAX.) 0.54 mW (CMOS level input) Part number Refresh cycle 2,048 cycles/128 ms Refresh CAS before RAS self refresh CAS before RAS refresh RAS only refresh Hidden refresh CAS before RAS refresh RAS only refresh Hidden refresh µPD42S17405L µPD4217405L 2,048 cycles/32 ms

- 8 mW (CMOS level input) The information in this document is subject to change without notice. Document No. M10068EJ6V0DS00 (6th edition) Date Published January 1997 N Printed in Japan The mark shows major revised points. © 1995 µPD42S17405L, 4217405L