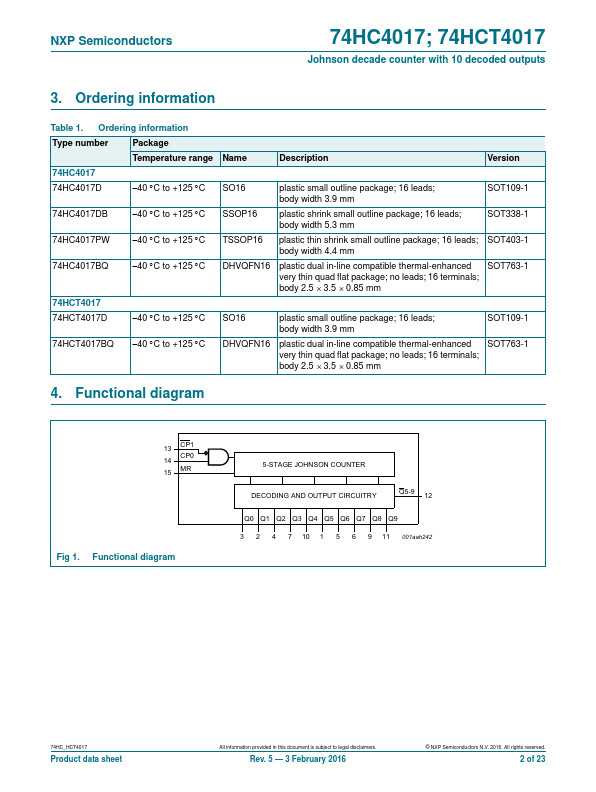

74HC4017 Description

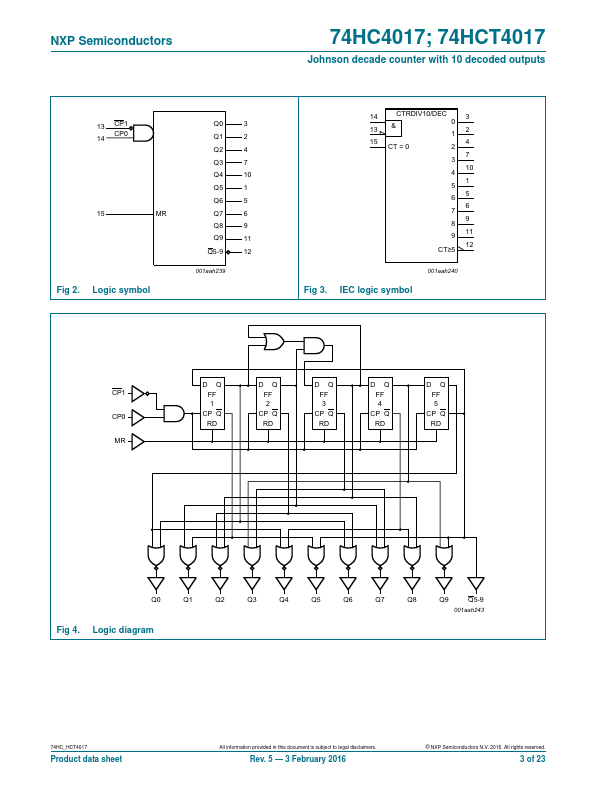

74HCT4017 is a 5-stage Johnson decade counter with 10 decoded outputs (Q0 to Q9), an output from the most significant flip-flop (Q5-9), two clock inputs (CP0 and CP1) and an overriding asynchronous master reset input (MR). The counter is advanced by either a LOW-to-HIGH transition at CP0 while CP1 is LOW or a HIGH-to-LOW transition at CP1 while CP0 is HIGH. When cascading counters, the Q5-9 output, which is LOW...

74HC4017 Key Features

- Wide supply voltage range from 2.0 V to 6.0 V

- Input levels

- For 74HC4017: CMOS level

- For 74HCT4017: TTL level

- plies with JEDEC standard no. 7 A

- ESD protection

- HBM JESD22-A114E exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Multiple package options

- Specified from 40 C to +85 C and from 40 C to +125 C