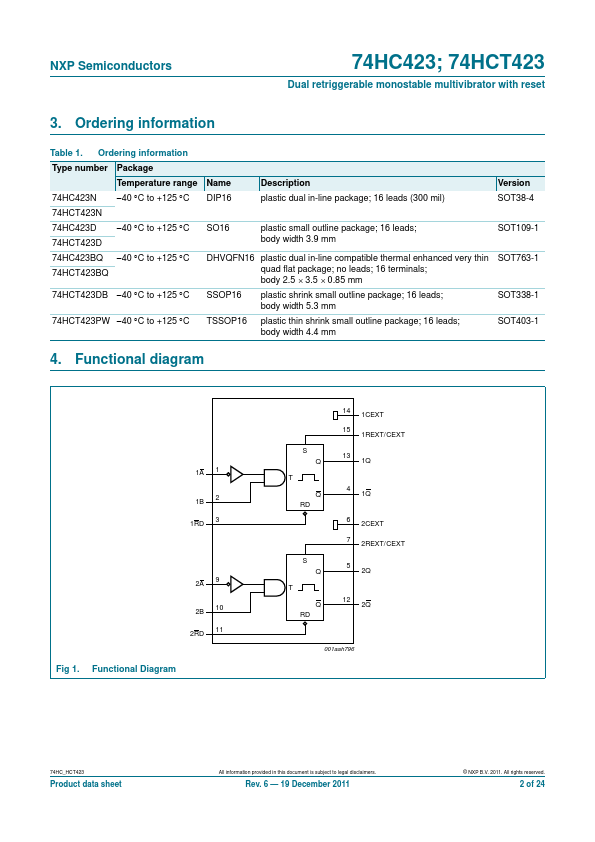

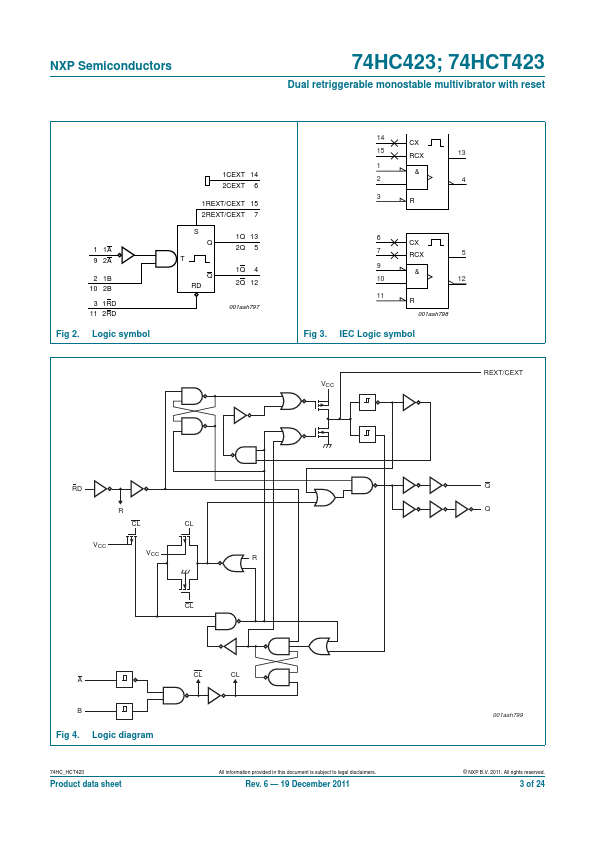

74HC423 Description

74HCT423 are high-speed Si-gate CMOS devices that are pin patible with Low power Schottky TTL (LSTTL). They are specified in pliance with JEDEC standard no. 74HCT423 dual retriggerable monostable multivibrator with reset has two methods of output pulse width control.

74HC423 Key Features

- DC triggered from active HIGH or active LOW inputs

- Retriggerable for very long pulses up to 100 % duty factor

- Direct reset terminates output pulse

- Schmitt-trigger action on all inputs except for the reset input

- plies with JEDEC standard no. 7A

- ESD protection

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Specified from 40 C to +85 C and from 40 C to +125 C

- 19 December 2011