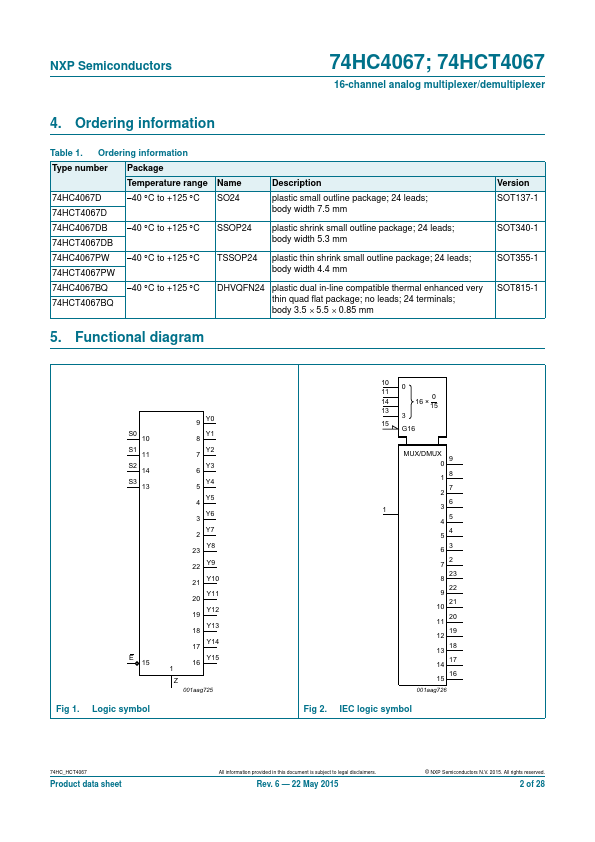

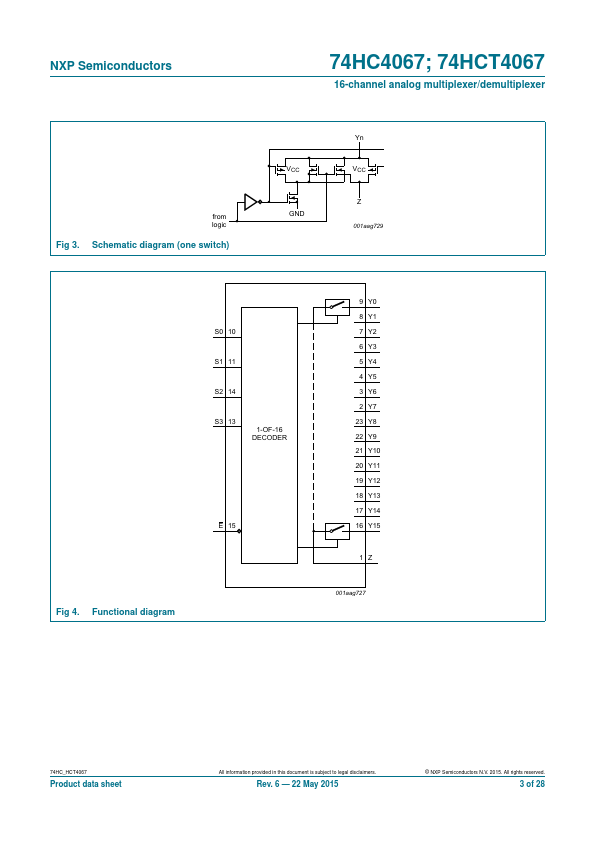

74HCT4067 Key Features

- Input levels S0, S1, S2, S3 and E inputs

- For 74HC4067: CMOS level

- For 74HCT4067: TTL level

- Low ON resistance

- 80 (typical) at VCC = 4.5 V

- 70 (typical) at VCC = 6.0 V

- 60 (typical) at VCC = 9.0 V

- Specified in pliance with JEDEC standard no. 7A

- ESD protection

- HBM JESD22-A114F exceeds 2000 V