74LVC3G04 Overview

The 74LVC3G04 is a high-performance, low-power, low-voltage, Si-gate CMOS device and superior to most advanced CMOS patible TTL families. Inputs can be driven from either 3.3 V or 5 V devices.

74LVC3G04 Key Features

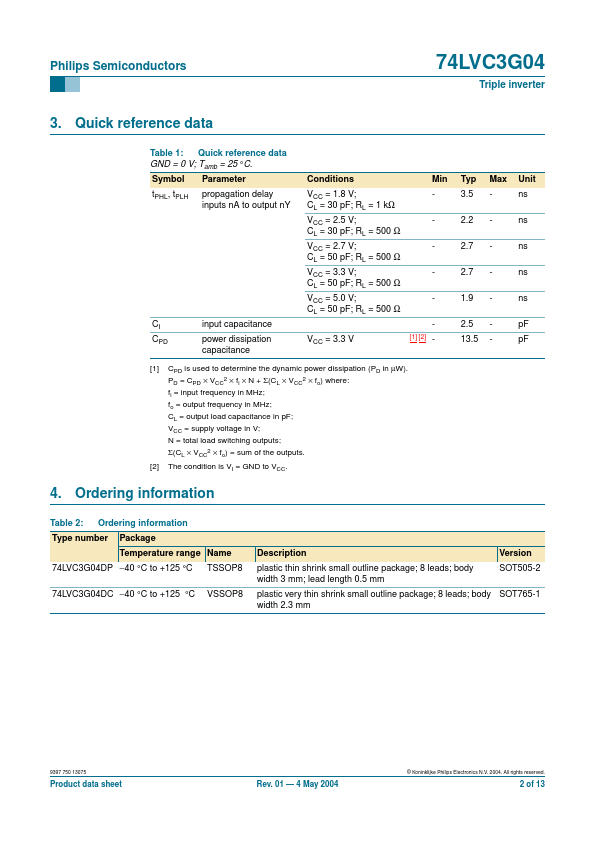

- Typ 3.5 2.2 2.7 2.7 1.9 2.5 13.5

- Unit ns ns ns ns ns pF pF

- CPD is used to determine the dynamic power dissipation (PD in µW). PD = CPD × VCC2 × fi × N + Σ(CL × VCC2 × fo) where: f

- 4 May 2004