P40C072

P40C072 is Secure smart card controller manufactured by NXP Semiconductors.

- Part of the P40C012 comparator family.

- Part of the P40C012 comparator family.

SmartMX2 P40 family

P40C012/040/072

Secure smart card controller

Rev. 3.0

- 24 April 2015 262830

Product short data sheet PANY PUBLIC

1. Introduction

1.1 Product overview

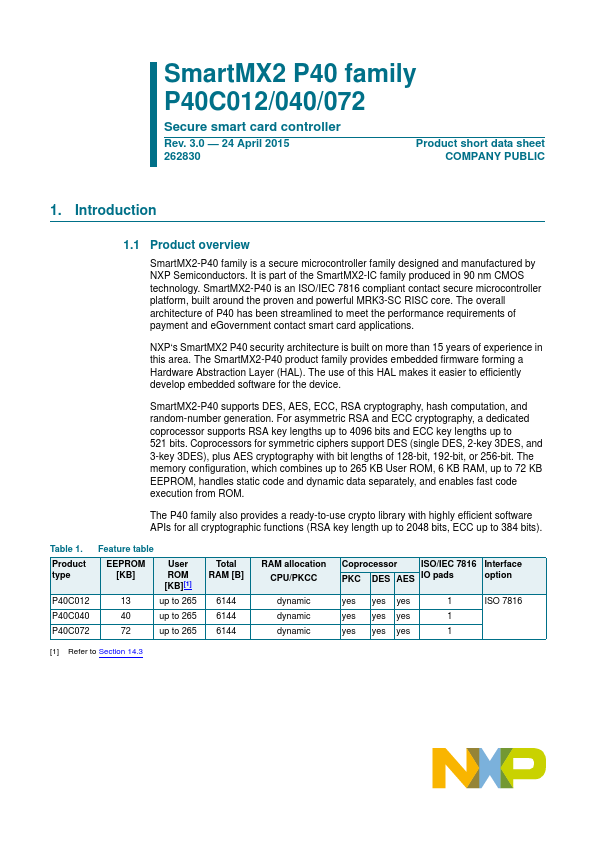

SmartMX2-P40 family is a secure microcontroller family designed and manufactured by NXP Semiconductors. It is part of the SmartMX2-IC family produced in 90 nm CMOS technology. SmartMX2-P40 is an ISO/IEC 7816 pliant contact secure microcontroller platform, built around the proven and powerful MRK3-SC RISC core. The overall architecture of P40 has been streamlined to meet the performance requirements of payment and eGovernment contact smart card applications.

NXP‘s SmartMX2 P40 security architecture is built on...