ADC1210S Key Features

- SNR, 70 dBFS; SFDR, 86 dBc Sample rate up to 125 Msps 12-bit pipelined ADC core Clock input divider by 2 for less jitter

- Single 3 V supply

- Flexible input voltage range: 1 V p-p to 2 V p-p

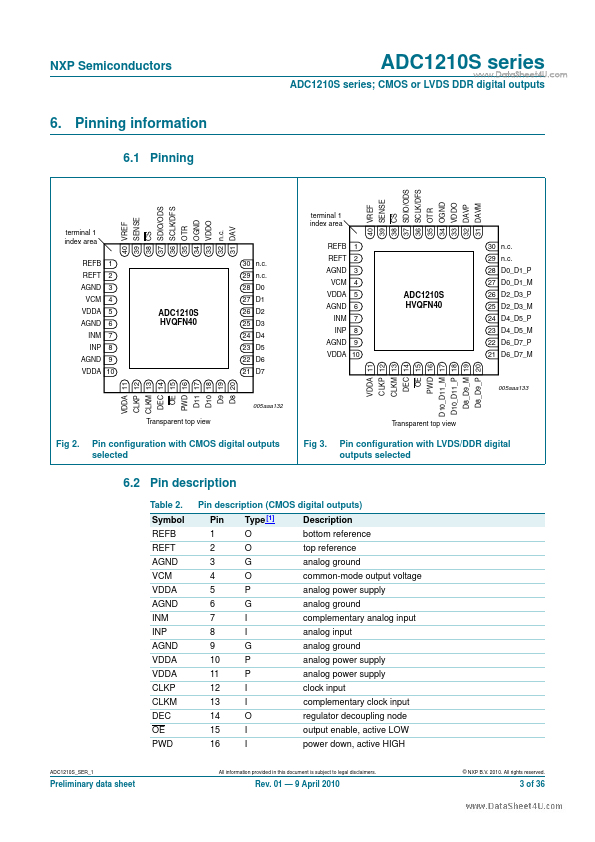

- CMOS or LVDS DDR digital outputs

- Pin patible with the ADC1410S series and the ADC1010 series

- HVQFN40 package

- Input bandwidth, 600 MHz Power dissipation, 430 mW at 80 Msps Serial Peripheral Interface (SPI) Duty cycle stabilizer

- Fast OuT of Range (OTR) detection

- INL ±0.25 LSB, DNL ±0.12 LSB

- Offset binary, two’s plement, gray code