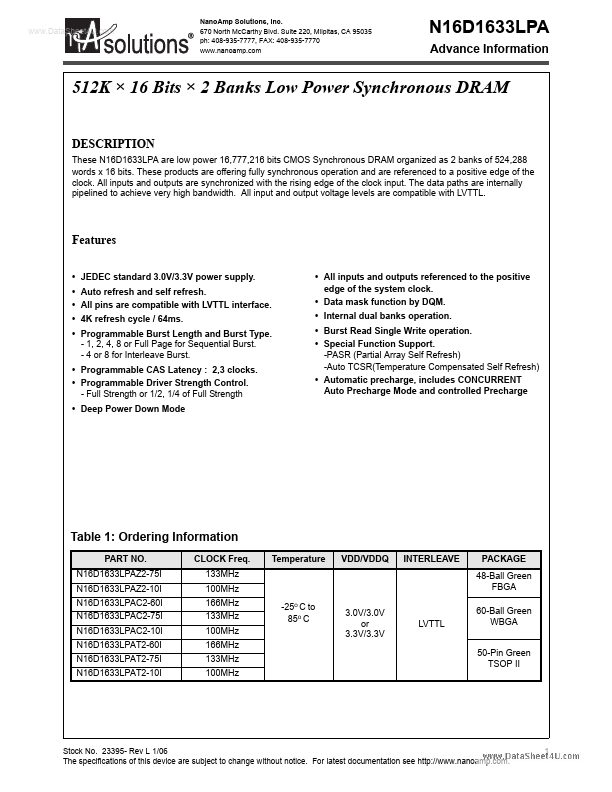

N16D1633LPA

Description

These N16D1633LPA are low power 16,777,216 bits CMOS Synchronous DRAM organized as 2 banks of 524,288 words x 16 bits. These products are offering fully synchronous operation and are referenced to a positive edge of the clock.

Key Features

- JEDEC standard 3.0V/3.3V power supply.

- Auto refresh and self refresh.

- All pins are compatible with LVTTL interface.

- 4K refresh cycle / 64ms.

- Programmable Burst Length and Burst Type. - 1, 2, 4, 8 or Full Page for Sequential Burst. - 4 or 8 for Interleave Burst.

- Programmable CAS Latency : 2,3 clocks.

- Programmable Driver Strength Control. - Full Strength or 1/2, 1/4 of Full Strength

- Deep Power Down Mode

- All inputs and outputs referenced to the positive edge of the system clock.

- Data mask function by DQM.