NT5CC512M8CN Overview

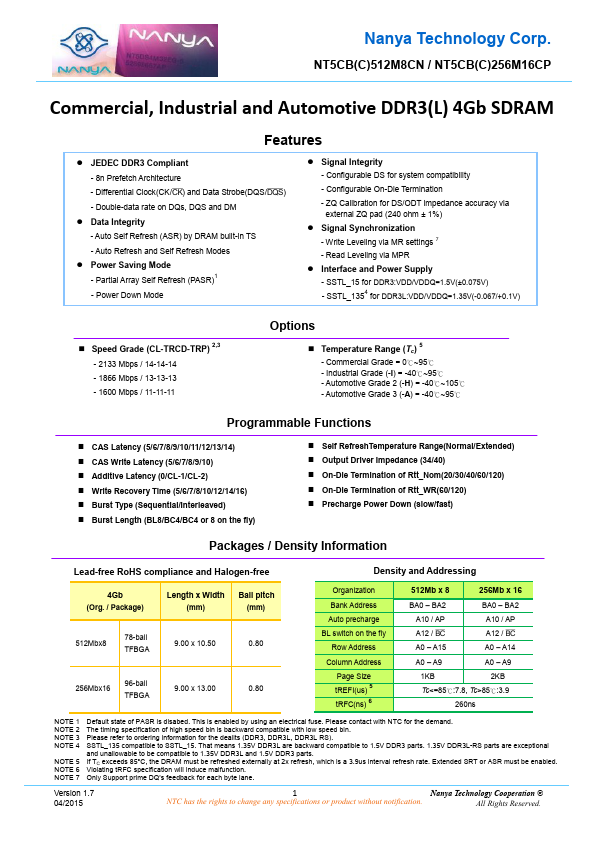

DDR3(L) 4Gb SDRAM NT5CB(C)512M8CN / NT5CB(C)256M16CP Nanya Technology Corp. NT5CB(C)512M8CN / NT5CB(C)256M16CP mercial, Industrial and Automotive DDR3(L) 4Gb SDRAM.

NT5CC512M8CN Key Features

- JEDEC DDR3 pliant

- 8n Prefetch Architecture

- Differential Clock(CK/) and Data Strobe(DQS/ )

- Double-data rate on DQs, DQS and DM

- Signal Integrity

- Configurable DS for system patibility

- Configurable On-Die Termination

- ZQ Calibration for DS/ODT impedance accuracy via external ZQ pad (240 ohm ± 1%)

- Data Integrity

- Auto Self Refresh (ASR) by DRAM built-in TS