100310

100310 is Low Skew 2:8 Differential Clock Driver manufactured by National Semiconductor.

Description

The 100310 is a low skew a- bit differential clock driver which is designed to select between two separate differen- tial clock inputs. The low output to output skew « 50 ps) is maintained for either clock input. A LOW on the select pin (SEL) selects CLKINA. CLKINA and a HIGH on the SEl pin selects the CLKINS. Cl KINS inputs.

The 100310 is ideal for those applications that need the ability to freely select between two clocks. or to maintain the ability to switch to an alternate or backup clock should a problem arise with the primary clock source.

A Vss output is provided for single-ended operation.

Features

- Low output to output skew

- Differential inputs and outputs

- Allows multiplexing between two clock inputs

- Voltage pensated operating range: -4.2V to -5.7V

Ordering Code: See Section 5

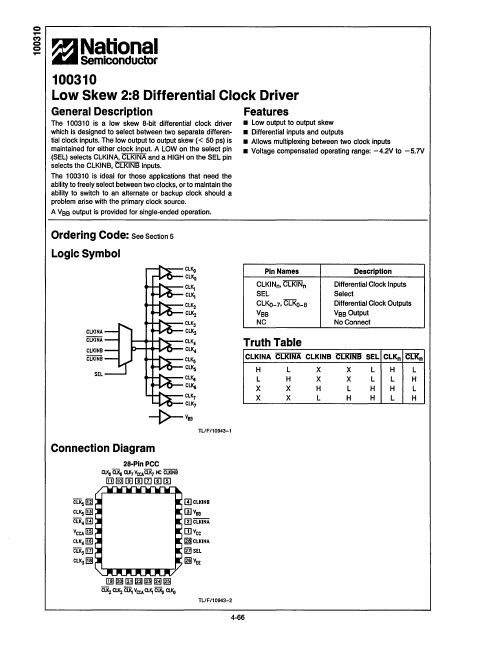

Logic Symbol

CLKINA Cl KINA CLKINB CLKINB

Cl Kg CLKg

CLKj CLKj

CLK2 CLK2 Cl K3 CLK3 CLK. CLK.

CLKs CLKs

CLKs CLKs

Cl K7 CLK7

--t>--vss

Tl/F/10943-1

Connection Diagram

28-Pln pcc rn Cl Ke Cl Ke ax7VCCAax7 NC Cl KINB

[TI [Q] [!] [l][IIIII

Pin Names

CLKINn- Cl KINn SEL

CLKo_7. CD<o-a

Vss NC

Description

Differential Clock Inputs Select Differential Clock Outputs Vss Output No Connect

Truth Table

Cl KINA Cl KINA Cl KINB Cl KINB SEl Cl Kn C[Kn

LH L...