54148 Overview

Description

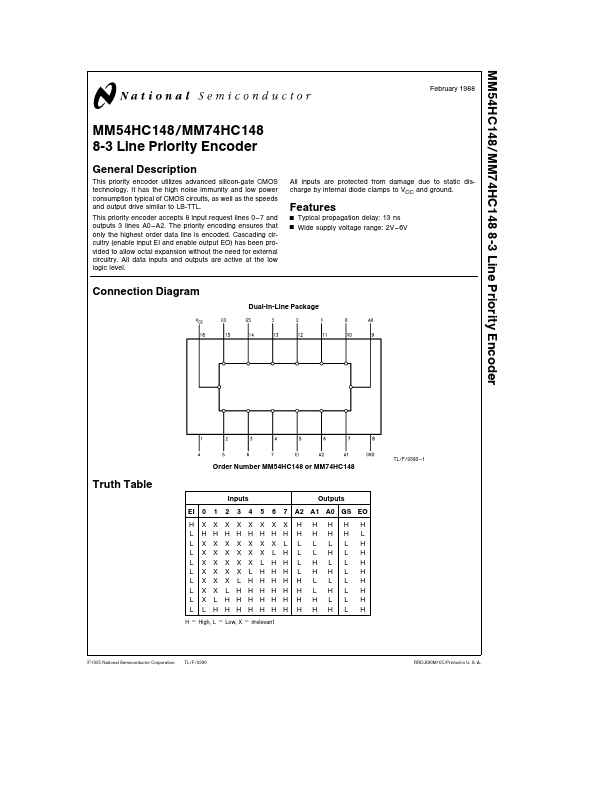

This priority encoder utilizes advanced silicon-gate CMOS technology It has the high noise immunity and low power consumption typical of CMOS circuits as well as the speeds and output drive similar to LB-TTL This priority encoder accepts 8 input request lines 0– 7 and outputs 3 lines A0–A2 The priority encoding ensures that only the highest order data line is encoded Cascading circuitry (enable input EI and enable output EO) has been provided to allow octal expansion without the need for external circuitry All data inputs and outputs are active at the low logic level All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.