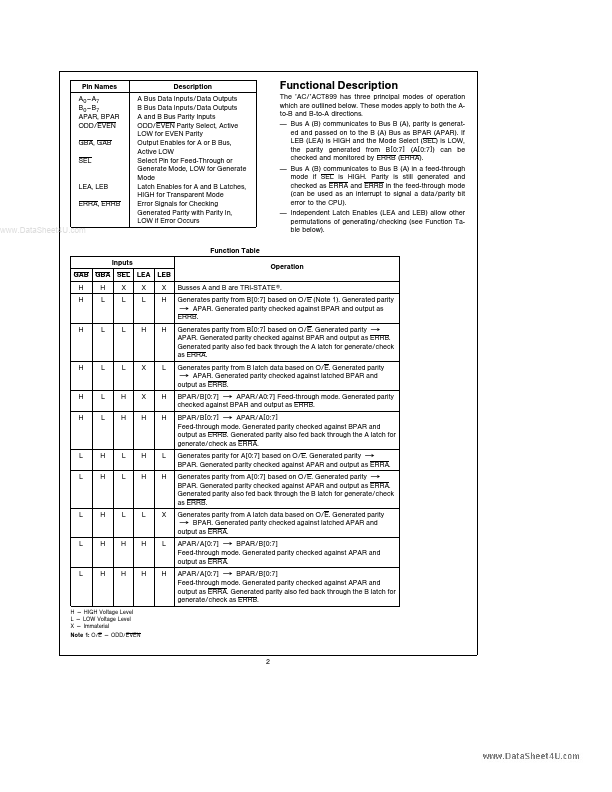

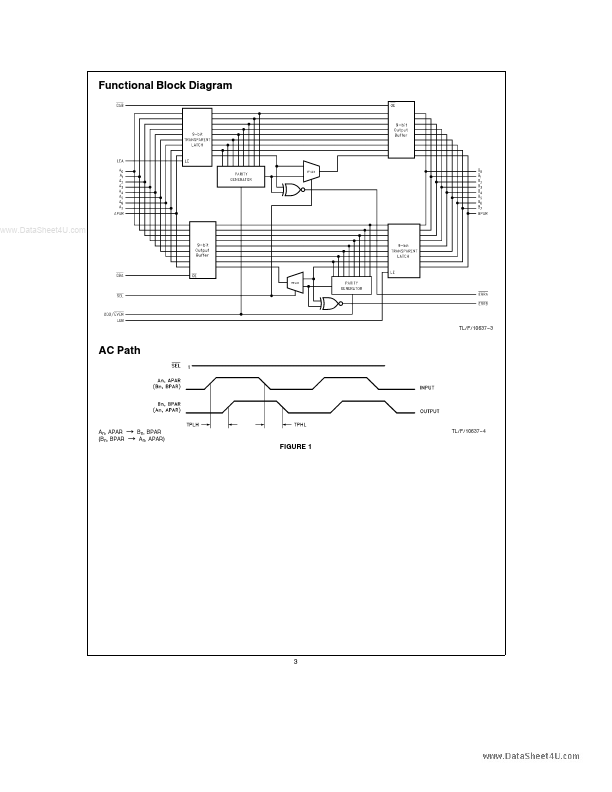

Datasheet Summary

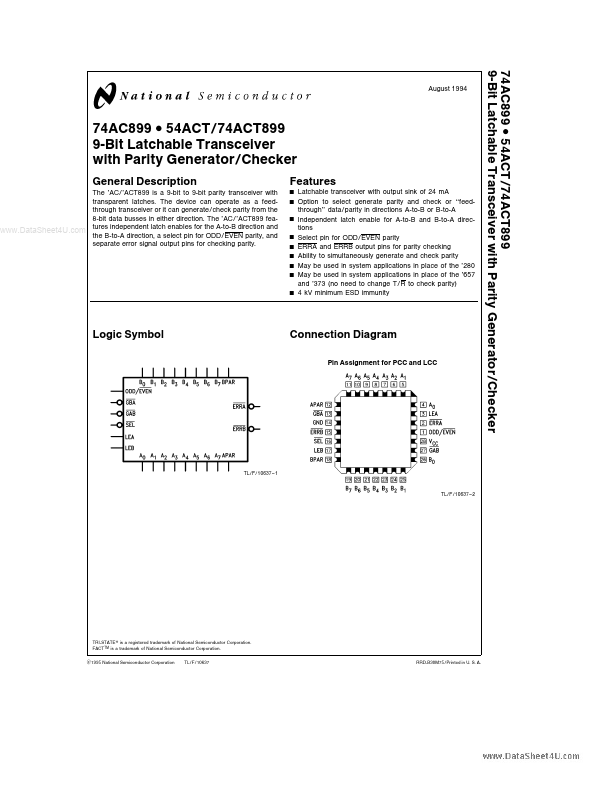

74AC899 54ACT 74ACT899 9-Bit Latchable Transceiver with Parity Generator Checker

August 1994

74AC899 54ACT 74ACT899 9-Bit Latchable Transceiver with Parity Generator Checker

General Description

The ’AC ’ACT899 is a 9-bit to 9-bit parity transceiver with transparent latches The device can operate as a feedthrough transceiver or it can generate check parity from the 8-bit data busses in either direction The ’AC ’ACT899 fea.. tures independent latch enables for the A-to-B direction and the B-to-A direction a select pin for ODD EVEN parity and separate error signal output pins for checking parity

Features

Y Y Y Y Y

Latchable transceiver with output sink of...