74ACQ377

74ACQ377 is Quiet Series Octal D Flip-Flop manufactured by National Semiconductor.

- Part of the 74ACTQ377 comparator family.

- Part of the 74ACTQ377 comparator family.

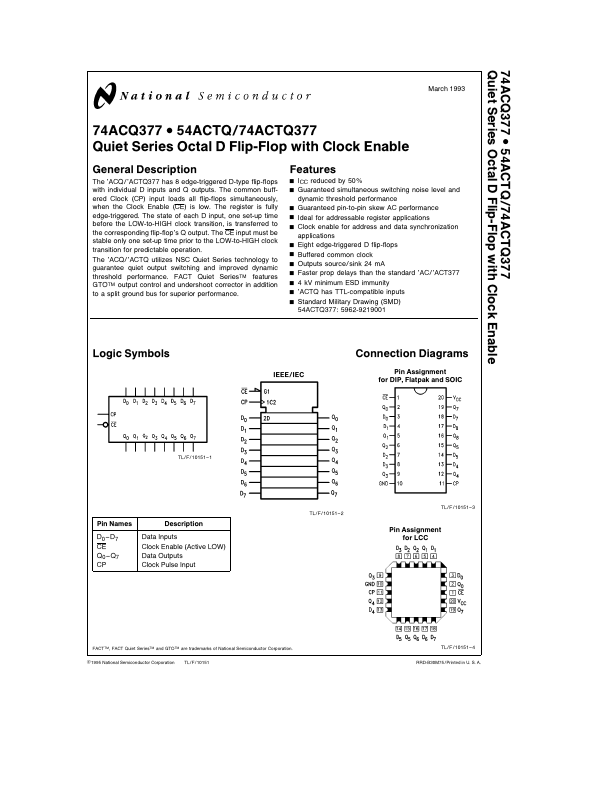

74ACQ377 54ACTQ 74ACTQ377

Quiet Series Octal D Flip-Flop with Clock Enable

March 1993

74ACQ377 54ACTQ 74ACTQ377

Quiet Series Octal D Flip-Flop with Clock Enable

General Description

The ’ACQ ’ACTQ377 has 8 edge-triggered D-type flip-flops with individual D inputs and Q outputs The mon buffered Clock (CP) input loads all flip-flops simultaneously when the Clock Enable (CE) is low The register is fully edge-triggered The state of each D input one set-up time before the LOW-to-HIGH clock transition is transferred to the corresponding flip-flop’s Q output The CE input must be stable only one set-up time prior to the LOW-to-HIGH clock transition for predictable operation

The ’ACQ ’ACTQ...