74F190

Description

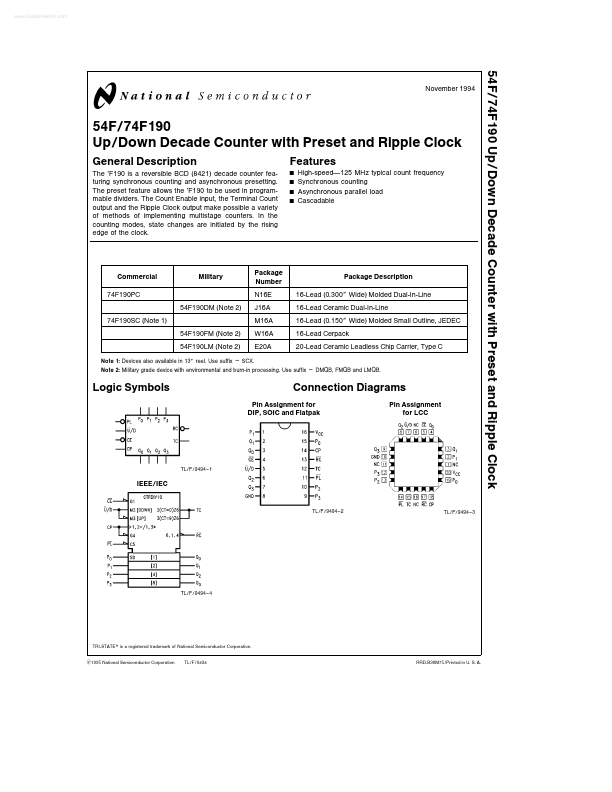

The ’F190 is a reversible BCD (8421) decade counter featuring synchronous counting and asynchronous presetting The preset feature allows the ’F190 to be used in programmable dividers The Count Enable input the Terminal Count output and the Ripple Clock output make possible a variety of methods of implementing multistage counters In the counting modes state changes are initiated by the rising edge of the clock.