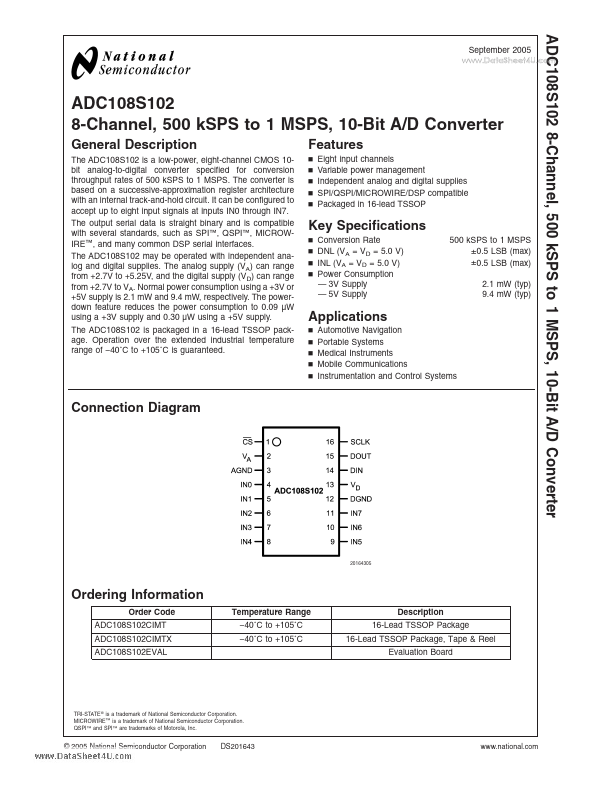

ADC108S102 Description

The ADC108S102 is a low-power, eight-channel CMOS 10bit analog-to-digital converter specified for conversion throughput rates of 500 kSPS to 1 MSPS. The converter is based on a successive-approximation register architecture with an internal track-and-hold circuit. It can be configured to accept up to eight input signals at inputs IN0 through IN7.

ADC108S102 Key Features

- 3V Supply

- 5V Supply 500 kSPS to 1 MSPS ± 0.5 LSB (max) ± 0.5 LSB (max) 2.1 mW (typ) 9.4 mW (typ)

ADC108S102 Applications

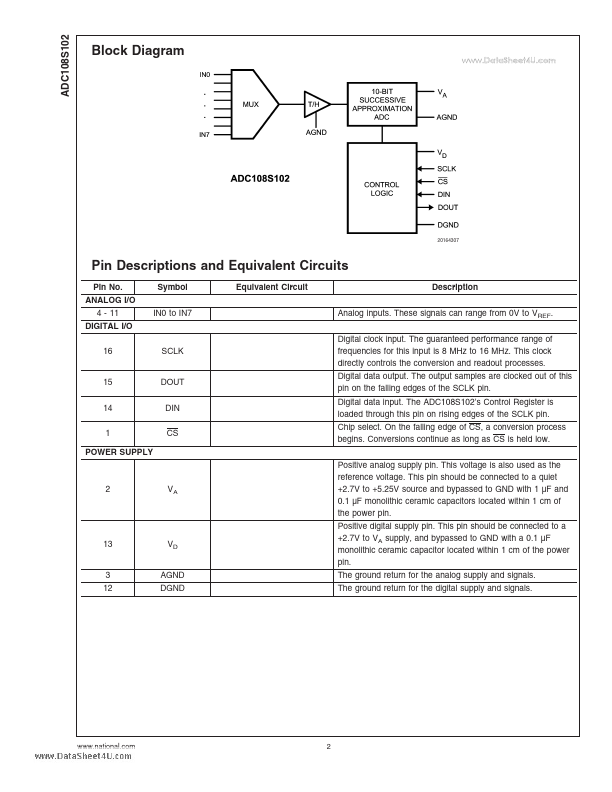

- 11 DIGITAL I/O 16 SCLK Digital clock input. The guaranteed performance range of frequencies for this input is 8 MHz to 16 MHz. This clock directly controls the