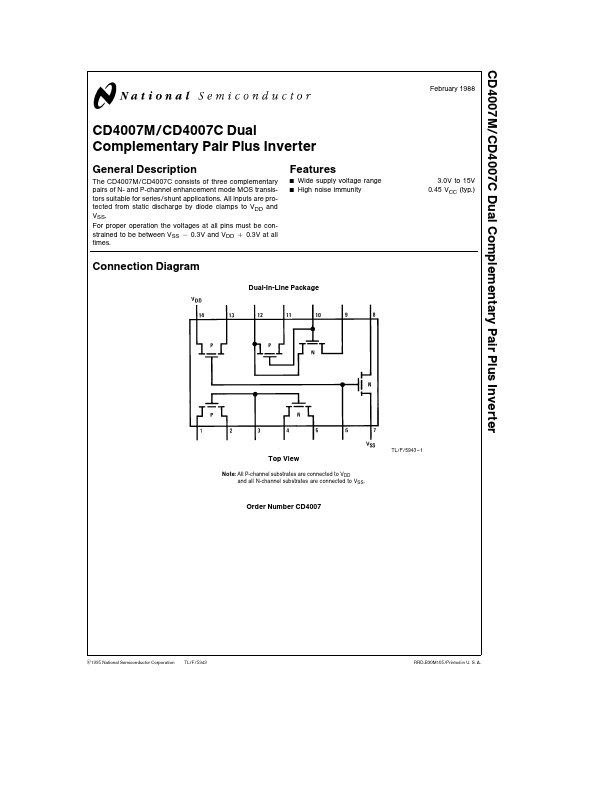

- Part: CD4007M

- Description: Dual Complementary Pair Plus Inverter

- Manufacturer: National Semiconductor

- Size: 100.61 KB

Other CD4007M Datasheets

| Manufacturer | Part Number | Description |

|---|---|---|

RCA

RCA |

CD4007A | CMOS Dual Complementary Pair Plus Inverter |

Intersil

Intersil |

CD4007A | CMOS Dual Complementary Pair Plus Inverter |

Texas Instruments

Texas Instruments |

CD4007AN | CMOS Dual Complementary Pair Plus Inverter |

| CD4007C | Dual Complementary Pair Plus Inverter | |

| CD4007CM | Dual Complementary Pair Plus Inverter |