DM7556

DM7556 is TRI-STATE Programmable Binary Counters manufactured by National Semiconductor.

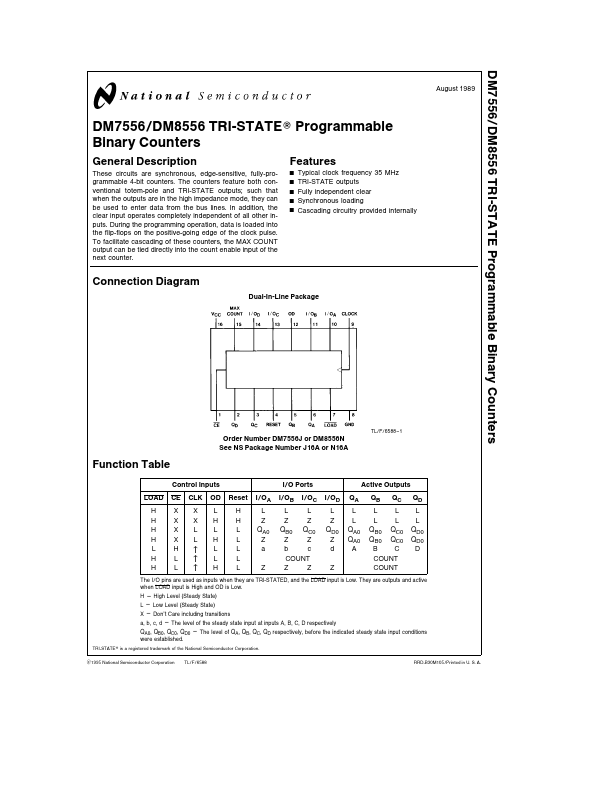

DM7556 DM8556 TRI-STATE Programmable Binary Counters

August 1989

DM7556 DM8556 TRI-STATE Programmable Binary Counters

General Description

These circuits are synchronous edge-sensitive fully-programmable 4-bit counters The counters feature both conventional totem-pole and TRI-STATE outputs such that when the outputs are in the high impedance mode they can be used to enter data from the bus lines In addition the clear input operates pletely independent of all other inputs During the programming operation data is loaded into the flip-flops on the positive-going edge of the clock pulse To facilitate cascading of these counters the MAX COUNT output can be tied directly into the count...