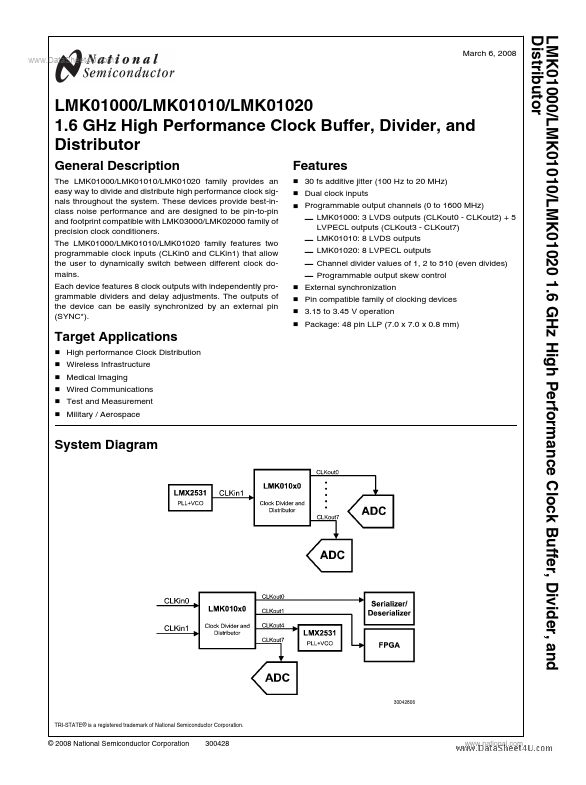

LMK01000 Description

The LMK01000/LMK01010/LMK01020 family provides an easy way to divide and distribute high performance clock signals throughout the system. These devices provide best-inclass noise performance and are designed to be pin-to-pin and footprint patible with LMK03000/LMK02000 family of precision clock conditioners. The LMK01000/LMK01010/LMK01020 family.

LMK01000 Key Features

- 30 fs additive jitter (100 Hz to 20 MHz)

- Dual clock inputs

- Programmable output channels (0 to 1600 MHz)

- LMK01000: 3 LVDS outputs (CLKout0

- CLKout2) + 5 LVPECL outputs (CLKout3

- CLKout7)

- LMK01010: 8 LVDS outputs

- LMK01020: 8 LVPECL outputs

- Channel divider values of 1, 2 to 510 (even divides)

- Programmable output skew control External synchronization Pin patible family of clocking devices 3.15 to 3.45 V operatio