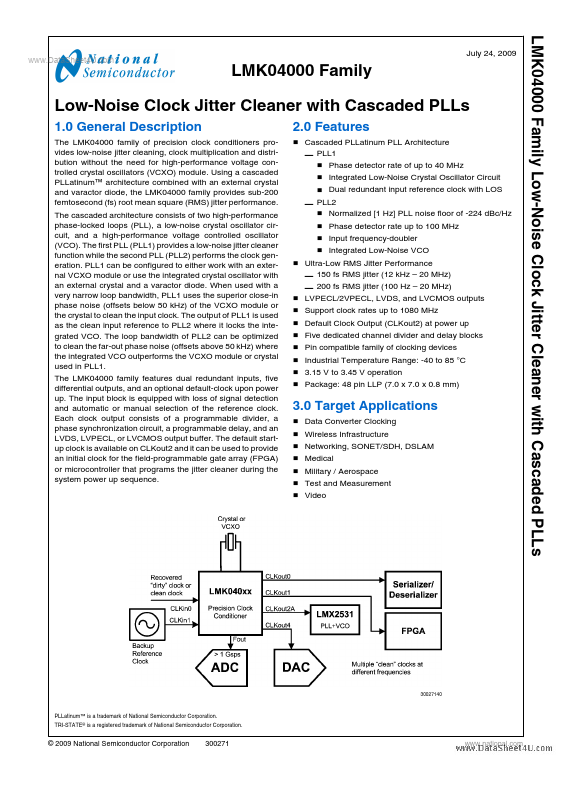

LMK04000 Description

The LMK04000 family of precision clock conditioners provides low-noise jitter cleaning, clock multiplication and distribution without the need for high-performance voltage controlled crystal oscillators (VCXO) module. Using a cascaded PLLatinum™ architecture bined with an external crystal and varactor diode, the LMK04000 family provides sub-200 femtosecond (fs) root mean square (RMS) jitter performance. The cascaded...

LMK04000 Key Features

- Cascaded PLLatinum PLL Architecture

- Phase detector rate of up to 40 MHz

- Integrated Low-Noise Crystal Oscillator Circuit

- Dual redundant input reference clock with LOS

- Normalized [1 Hz] PLL noise floor of -224 dBc/Hz

- Phase detector rate up to 100 MHz

- Input frequency-doubler

- Integrated Low-Noise VCO Ultra-Low RMS Jitter Performance

- 150 fs RMS jitter (12 kHz

- 20 MHz)