PC8374L

Description

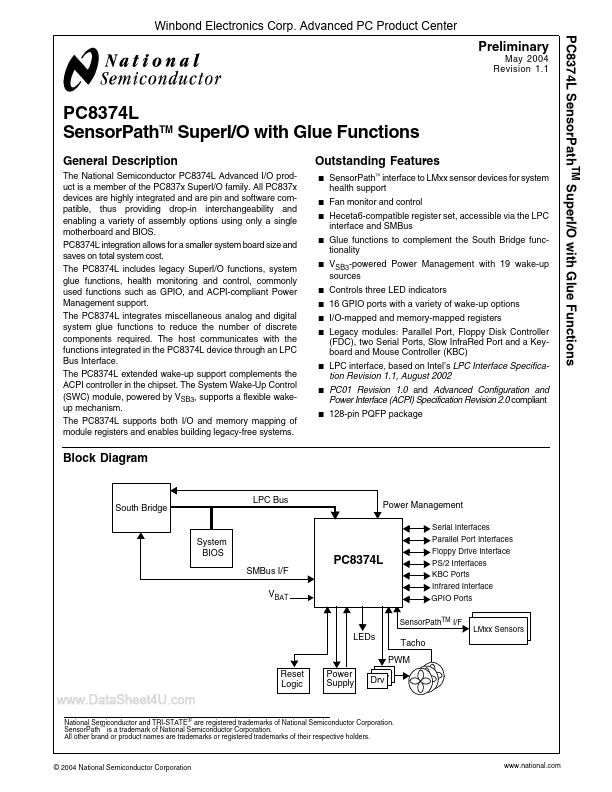

The National Semiconductor PC8374L Advanced I/O product is a member of the PC837x Super I/O family. All PC837x devices are highly integrated and are pin and software patible, thus providing drop-in interchangeability and enabling a variety of assembly options using only a single motherboard and BIOS. PC8374L integration allows for a smaller system board size and saves on total system cost. The PC8374L includes legacy Super I/O functions, system glue functions, health monitoring and control, monly used functions such as GPIO, and ACPI-pliant Power Management support. The PC8374L integrates miscellaneous analog and digital system glue functions to reduce the number of discrete ponents required. The host municates with the functions integrated in the PC8374L device through an LPC Bus Interface. The PC8374L extended wake-up support plements the ACPI controller in the chipset. The System Wake-Up Control (SWC) module, powered by VSB3, supports a flexible wakeup mechanism. The...