SCAN18373T

Overview

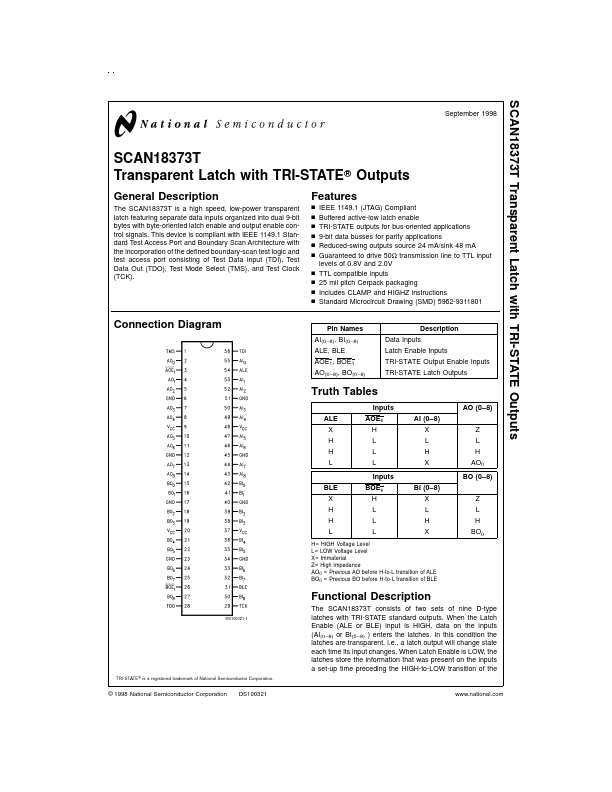

The SCAN18373T is a high speed, low-power transparent latch featuring separate data inputs organized into dual 9-bit bytes with byte-oriented latch enable and output enable control signals. This device is compliant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture with the incorporation of the defined boundary-scan test logic and test access port consisting of Test Data Input (TDI), Test Data Out (TDO), Test Mode Select (TMS), and Test Clock (TCK).

- n n n n n n n n

- IEEE 1149.1 (JTAG) Compliant Buffered active-low latch enable TRI-STATE outputs for bus-oriented applications 9-bit data busses for parity applications Reduced-swing outputs source 24 mA/sink 48 mA Guaranteed to drive 50Ω transmission line to TTL input levels of 0.8V and 2.0V TTL compatible inputs 25 mil pitch Cerpack packaging Includes CLAMP and HIGHZ instructions Standard Microcircuit Drawing (SMD) 5962-9311801 Connection Diagram Pin Names AI(0-8), BI(0-8) ALE, BLE AOE1, BOE1 AO(0-8), BO(0-8)