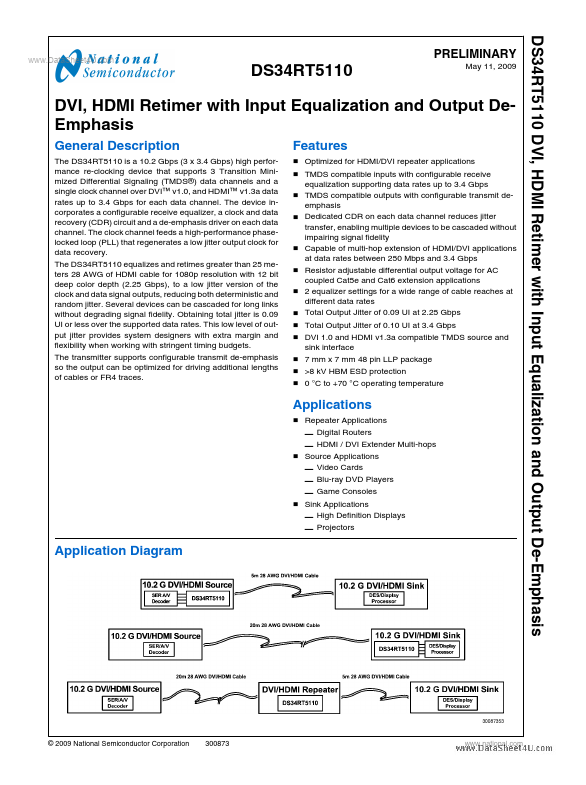

DS34RT5110 Description

The DS34RT5110 is a 10.2 Gbps (3 x 3.4 Gbps) high performance re-clocking device that supports 3 Transition Minimized Differential Signaling (TMDS®) data channels and a single clock channel over DVI™ v1.0, and HDMI™ v1.3a data rates up to 3.4 Gbps for each data channel. The device incorporates a configurable receive equalizer, a clock and data recovery (CDR) circuit and a de-emphasis driver on each data channel. The...

DS34RT5110 Key Features

- Optimized for HDMI/DVI repeater

DS34RT5110 Applications

- TMDS patible inputs with configurable receive

- TMDS patible outputs with configurable transmit de- Dedicated CDR on each data channel reduces jitter