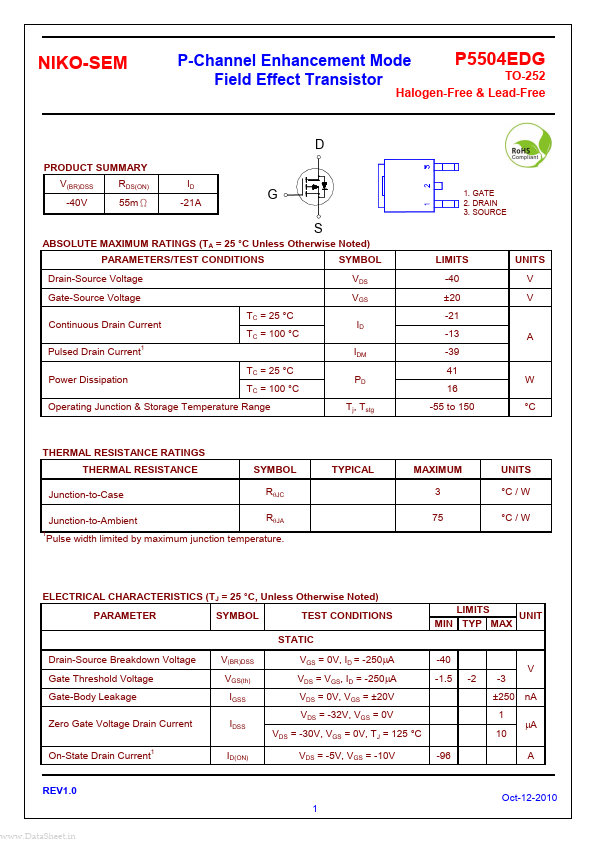

P5504EDG Description

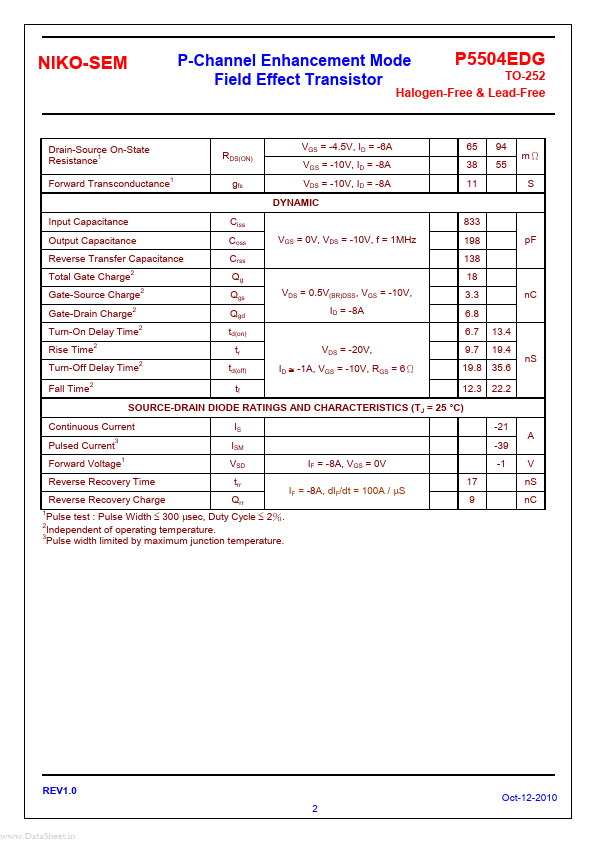

NIKO-SEM P-Channel Enhancement Mode Field Effect Transistor P5504EDG TO-252 Halogen-Free & Lead-Free D PRODUCT SUMMARY V(BR)DSS -40V RDS(ON) 55mΩ ID -21A G S 1. Pulse Width ≤ 300 µsec, Duty Cycle ≤ 2%. Independent of operating temperature.