SM5921A

Key Features

- Intrinsic delay (common to all channels, default = 0 samples, 16-sample units)

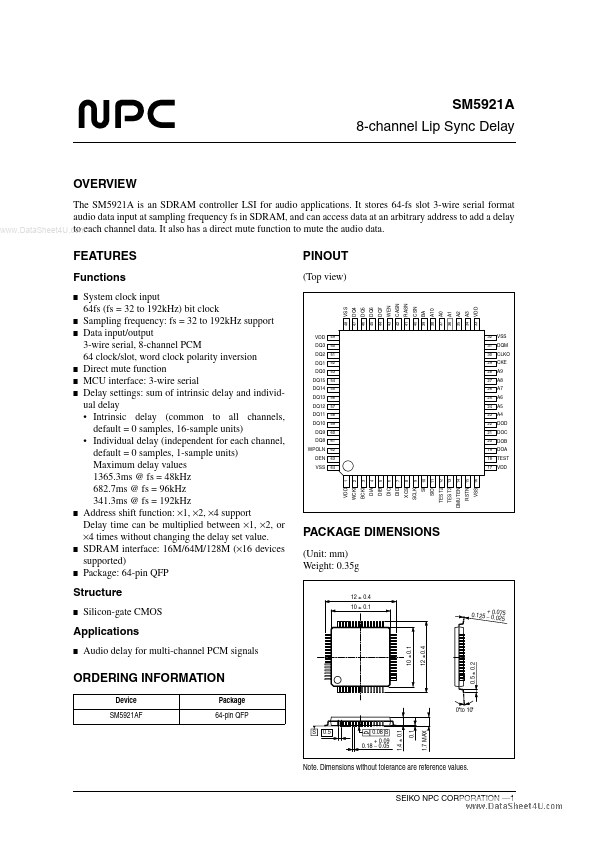

- Individual delay (independent for each channel, default = 0 samples, 1-sample units) Maximum delay values 1365.3ms @ fs = 48kHz 682.7ms @ fs = 96kHz 341.3ms @ fs = 192kHz Address shift function: ×1, ×2, ×4 support Delay time can be multiplied between ×1, ×2, or ×4 times without changing the delay set value. SDRAM interface: 16M/64M/128M (×16 devices supported) Package: 64-pin QFP DQ4 DQ5 DQ6 DQ7 VSS A10 BA A0 A1 A2 35 48 47 46 45 44 43 42 41 40 39 38 37 36 34 A3