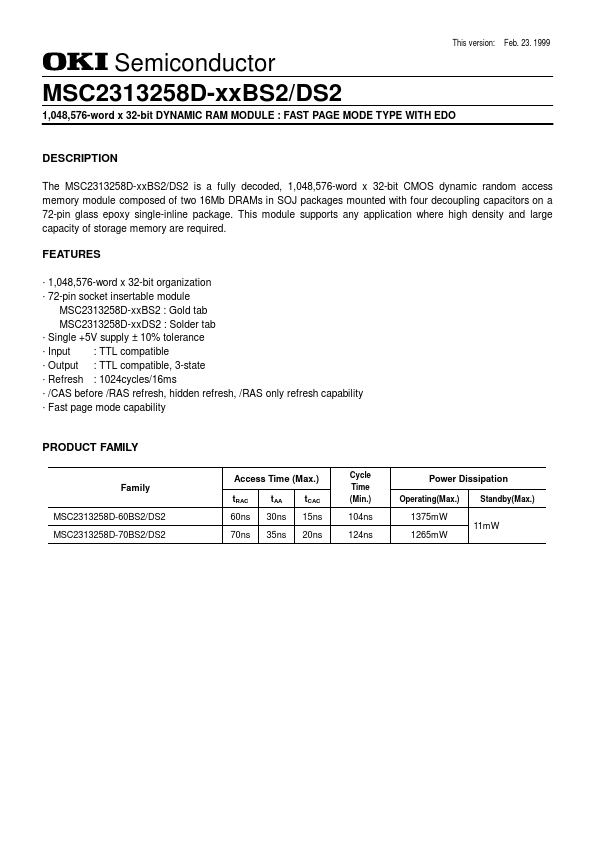

MSC2313258D

Overview

The MSC2313258D-xxBS2/DS2 is a fully decoded, 1,048,576-word x 32-bit CMOS dynamic random access memory module composed of two 16Mb DRAMs in SOJ packages mounted with four decoupling capacitors on a 72-pin glass epoxy single-inline package. This module supports any application where high density and large capacity of storage memory are required.

- 1,048,576-word x 32-bit organization

- 72-pin socket insertable module MSC2313258D-xxBS2 : Gold tab MSC2313258D-xxDS2 : Solder tab

- Single +5V supply ± 10% tolerance

- Input : TTL compatible

- Output : TTL compatible, 3-state

- Refresh : 1024cycles/16ms

- /CAS before /RAS refresh, hidden refresh, /RAS only refresh capability

- Fast page mode capability