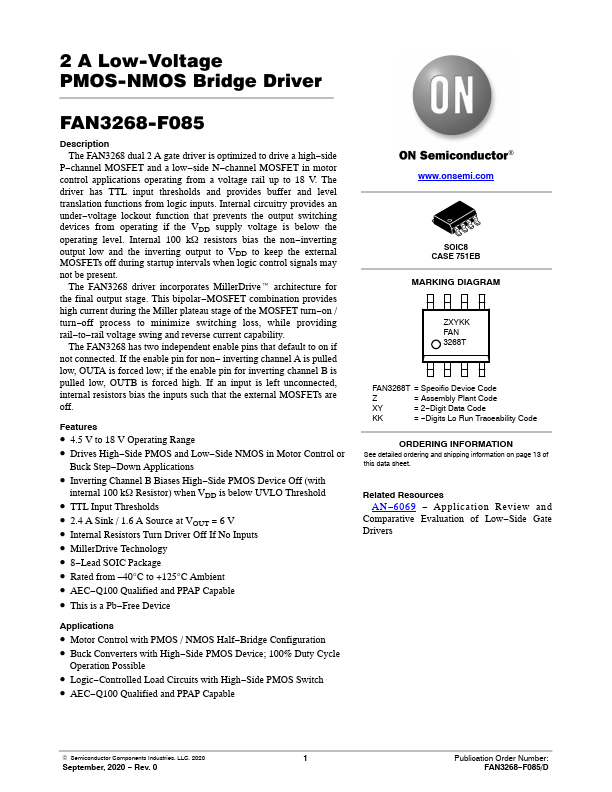

FAN3268-F085

Overview

- 4.5 V to 18 V Operating Range

- Drives High-Side PMOS and Low-Side NMOS in Motor Control or Buck Step-Down Applications

- Inverting Channel B Biases High-Side PMOS Device Off (with internal 100 kW Resistor) when VDD is below UVLO Threshold

- TTL Input Thresholds

- 2.4 A Sink / 1.6 A Source at VOUT = 6 V

- Internal Resistors Turn Driver Off If No Inputs

- MillerDrive Technology

- 8-Lead SOIC Package

- Rated from -40°C to +125°C Ambient

- AEC-Q100 Qualified and PPAP Capable