Datasheet Summary

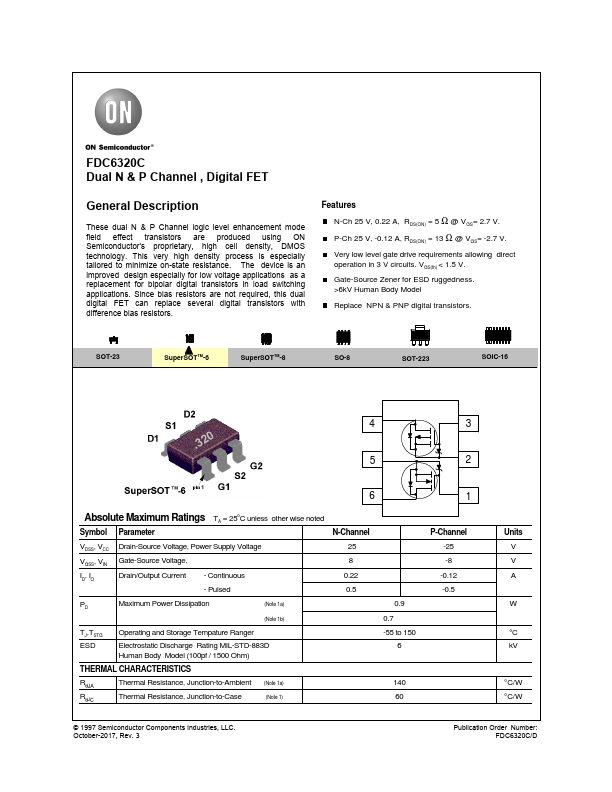

FDC6320C Dual N & P Channel , Digital FET

General Description

These dual N & P Channel logic level enhancement mode field effect transistors are produced using ON Semiconductor's proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimize on-state resistance. The device is an improved design especially for low voltage applications as a replacement for bipolar digital transistors in load switching applications. Since bias resistors are not required, this dual digital FET can replace several digital transistors with difference bias resistors.

Features

N-Ch 25 V, 0.22 A, RDS(ON) = 5 Ω @ VGS= 2.7 V.

P-Ch 25 V, -0.12 A, RDS(ON) = 13 Ω @...