NB100ELT23L Overview

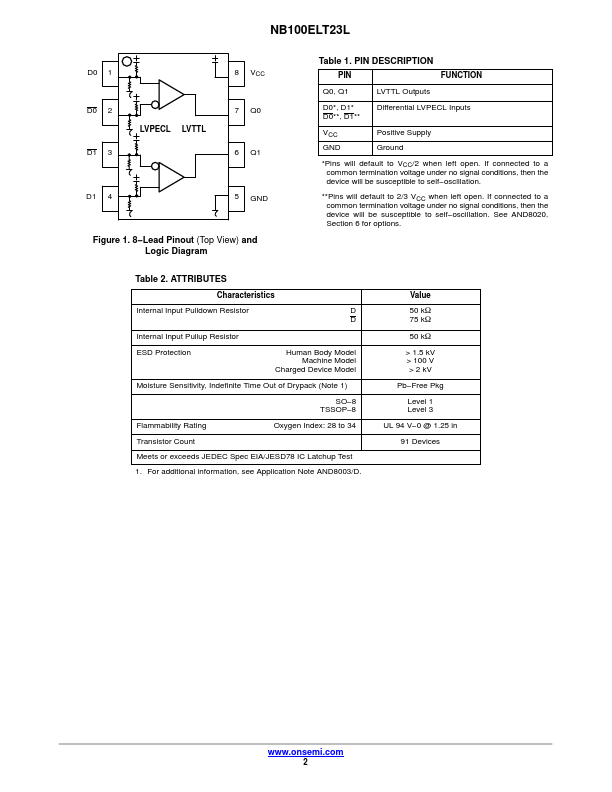

NB100ELT23L 3.3V Dual Differential LVPECL/LVDS to LVTTL Translator The NB100ELT23L is a dual differential LVPECL/LVDS to LVTTL translator. Because LVPECL (Positive ECL) or LVDS levels are used, only +3.3 V and ground are required. The small outline 8-lead package and the dual gate design of the ELT23L makes it ideal for applications which require the translation of a clock and a data signal.

NB100ELT23L Key Features

- 2.1 ns Typical Propagation Delay

- Maximum Operating Frequency > 160 MHz

- 24 mA LVTTL Outputs

- Operating Range: VCC = 3.0 V to 3.6 V with GND = 0 V

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS