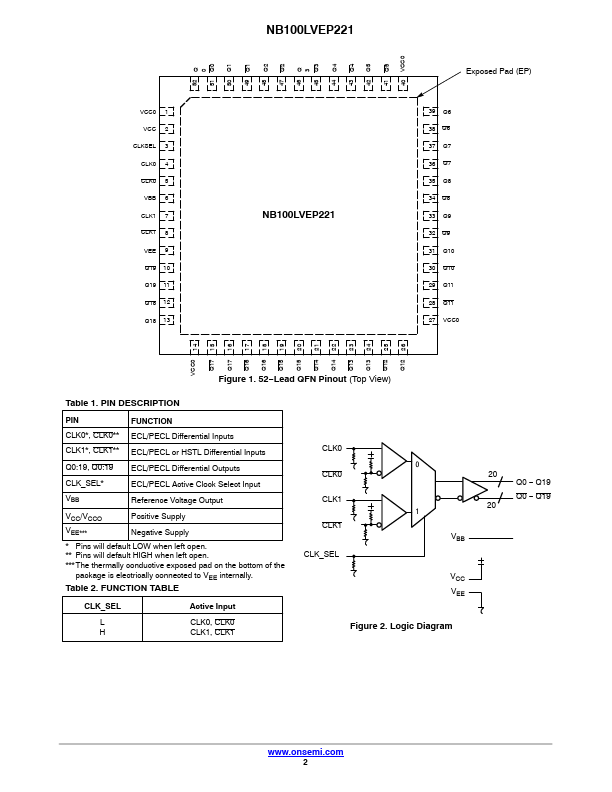

NB100LVEP221 Overview

The NB100LVEP221 is a low skew 2:1:20 differential clock driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The two clock inputs are differential ECL/PECL; CLK1/CLK1 can also receive HSTL signal levels.

NB100LVEP221 Key Features

- 15 ps Typical Output-to-Output Skew

- 40 ps Typical Device-to-Device Skew

- Jitter Less than 2 ps RMS

- Maximum Frequency > 1.0 GHz Typical

- Thermally Enhanced 52-Lead QFN Package

- VBB Output

- 540 ps Typical Propagation Delay

- LVPECL and HSTL Mode Operating Range

- NECL Mode Operating Range

- Q Output will Default Low with Inputs Open or at VEE