NB100LVEP222 Overview

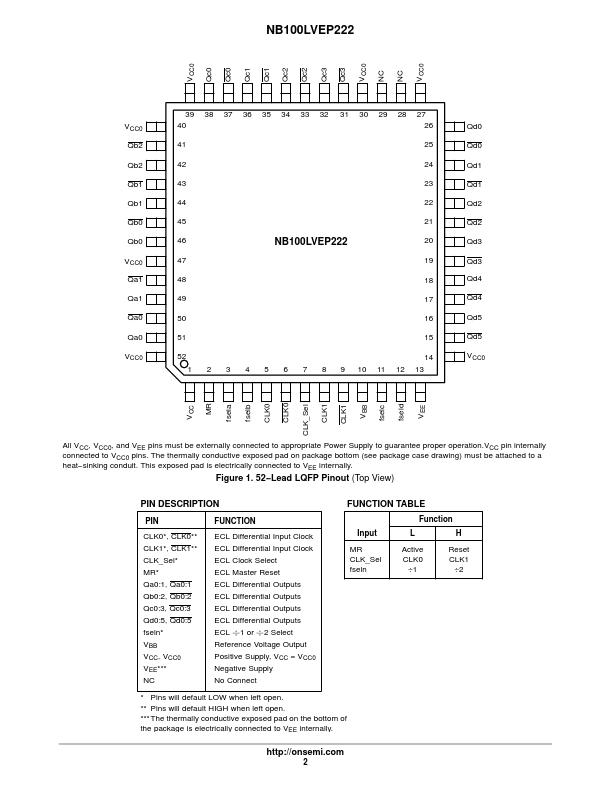

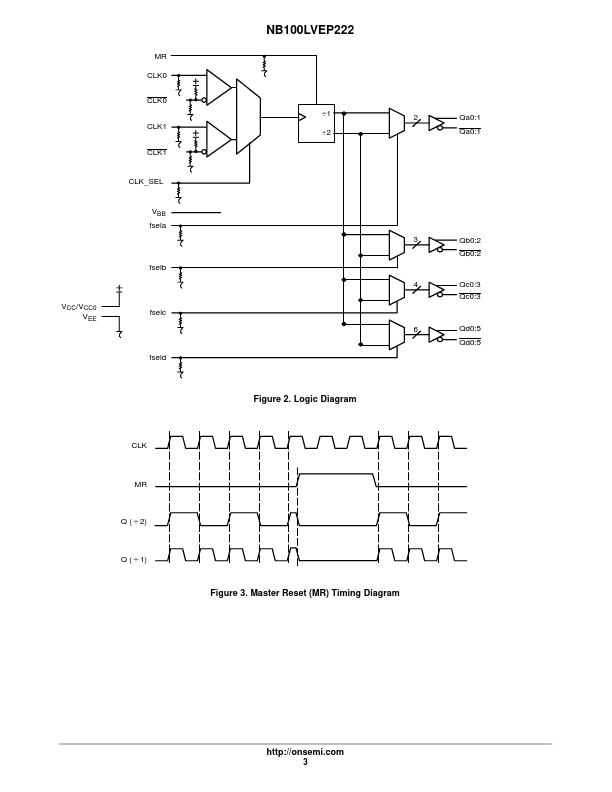

The LVECL/LVPECL input signal pairs can be used in a differential configuration or single−ended (with VBB output reference bypassed and connected to the unused input of a pair). Either of two fully differential clock inputs may be selected. Each of the four output banks of 2, 3, 4, and 6 differential pairs may be independently configured to fanout 1X or 1/2X of the input frequency.