NB100LVEP224 Overview

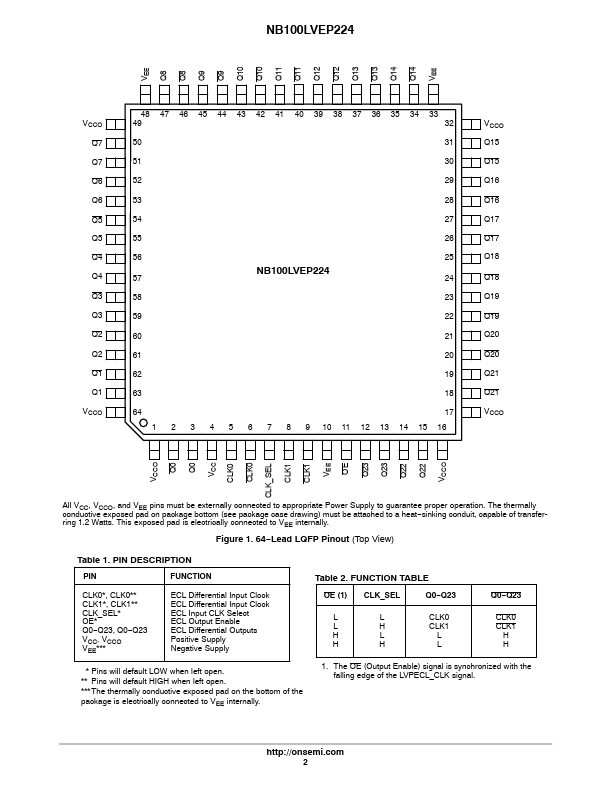

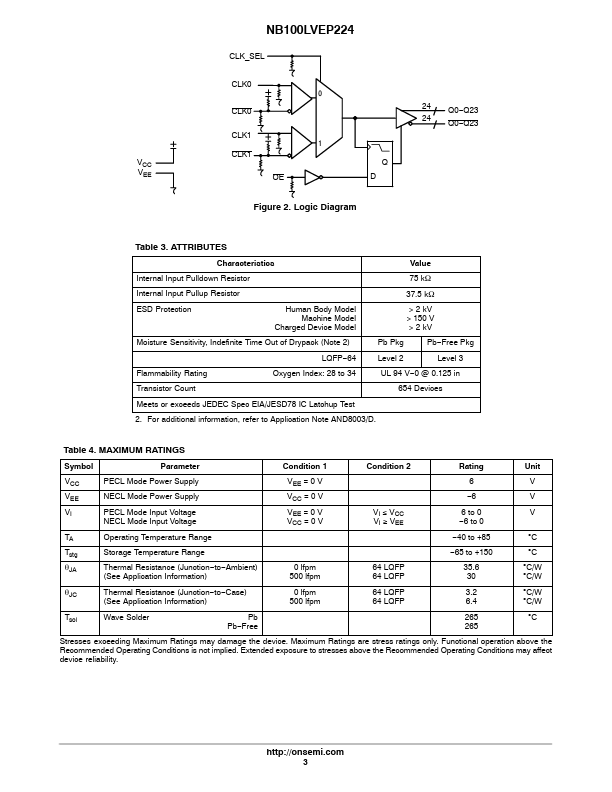

MARKING DIAGRAM The NB100LVEP224 is a low skew 1−to−24 differential clock driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The part is designed for use in low voltage applications which require a large number of outputs to drive precisely aligned low skew signals to their destination. The two clock inputs are differential ECL/PECL and they are selected by the...

NB100LVEP224 Key Features

- For additional marking information, refer to Application Note AND8002/D

- Internal Input Pulldown Resistors Q Output will Default Low with Inputs Open or at VEE Thermally Enhanced 64-Lead LQFP C

- For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering

NB100LVEP224 Applications

- For additional marking information, refer to Application Note AND8002/D